Tool/software:

Hi,

We are having considerable difficulty getting the lanes to link properly with the AFE7950 in a custom design. We are clocking the AFE7950 with LMK04828B. Our JESD lanes go to a Zynq SoC.

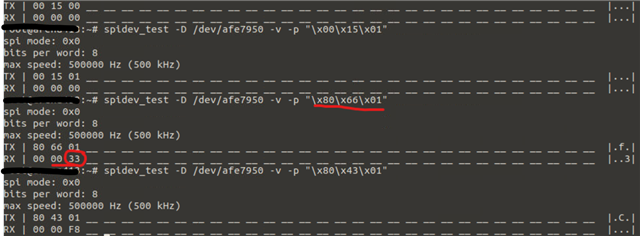

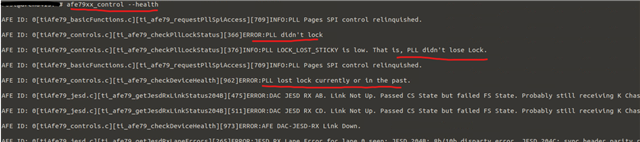

From the CAFE API, we receive conflicting indications that the the PLL in the AFE7950 is locked.

Additionally, some of lanes make it partially through the link sequence, passing clock sync (CS) but failing frame sync (FS).

afe79xx_control --health

AFE ID: 0[tiAfe79_basicFunctions.c][ti_afe79_requestPllSpiAccess][709]INFO:PLL Pages SPI control relinquished.

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkPllLockStatus][366]ERROR:PLL didn't lock

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkPllLockStatus][376]INFO:PLL LOCK_LOST_STICKY is low. That is, PLL didn't lose Lock.

AFE ID: 0[tiAfe79_basicFunctions.c][ti_afe79_requestPllSpiAccess][709]INFO:PLL Pages SPI control relinquished.

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][962]ERROR:PLL lost lock currently or in the past.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLinkStatus204B][475]ERROR:DAC JESD RX AB. Link Not Up. Passed CS State but failed FS State. Probably still receiving K Chas

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLinkStatus204B][511]ERROR:DAC JESD RX CD. Link Not Up. Passed CS State but failed FS State. Probably still receiving K Chas

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][973]ERROR:AFE DAC-JESD-RX Link Down.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 0 seen: JESD 204B: 8b/10b disparty error. JESD 204C: sync_header_parity_r

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 0 seen: JESD 204B: 8b/10b not-in-table code error. JESD 204C: sync_header

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 0 seen: code synchronization error

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 0 seen: elastic buffer match error. The first no-/K/ does not match 'mats

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneFifoErrors][310]ERROR:SerDes Rx Lane 0 got LOS error. There may be a SerDes Eye issue.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneFifoErrors][315]ERROR:SerDes Rx Lane 0 got FIFO Error. There may be a SerDes Eye issue or FIFO offset issue.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 1 seen: JESD 204B: 8b/10b disparty error. JESD 204C: sync_header_parity_r

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 1 seen: JESD 204B: 8b/10b not-in-table code error. JESD 204C: sync_header

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 1 seen: code synchronization error

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 1 seen: elastic buffer match error. The first no-/K/ does not match 'mats

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneFifoErrors][310]ERROR:SerDes Rx Lane 1 got LOS error. There may be a SerDes Eye issue.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneFifoErrors][315]ERROR:SerDes Rx Lane 1 got FIFO Error. There may be a SerDes Eye issue or FIFO offset issue.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 4 seen: JESD 204B: 8b/10b disparty error. JESD 204C: sync_header_parity_r

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 4 seen: JESD 204B: 8b/10b not-in-table code error. JESD 204C: sync_header

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 4 seen: code synchronization error

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 4 seen: elastic buffer match error. The first no-/K/ does not match 'mats

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneFifoErrors][310]ERROR:SerDes Rx Lane 4 got LOS error. There may be a SerDes Eye issue.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 5 seen: JESD 204B: 8b/10b disparty error. JESD 204C: sync_header_parity_r

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 5 seen: JESD 204B: 8b/10b not-in-table code error. JESD 204C: sync_header

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 5 seen: code synchronization error

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdRxLaneErrors][265]ERROR:JESD RX Lane Error for lane 5 seen: elastic buffer match error. The first no-/K/ does not match 'mats

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][984]ERROR:AFE DAC-JESD-RX has some errors triggered.

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][1001]INFO:AFE ADC-JESD-TX AB has no Errors triggered.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdTxFifoErrors][914]ERROR:JESD TX Lane Serdes FIFO Error for lane 0. SerDes PLL isn't locked or the FIFO offset setting is inc.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdTxFifoErrors][914]ERROR:JESD TX Lane Serdes FIFO Error for lane 1. SerDes PLL isn't locked or the FIFO offset setting is inc.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdTxFifoErrors][914]ERROR:JESD TX Lane Serdes FIFO Error for lane 2. SerDes PLL isn't locked or the FIFO offset setting is inc.

AFE ID: 0[tiAfe79_jesd.c][ti_afe79_getJesdTxFifoErrors][914]ERROR:JESD TX Lane Serdes FIFO Error for lane 3. SerDes PLL isn't locked or the FIFO offset setting is inc.

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][1006]ERROR:AFE ADC-JESD-TX CD has some errors triggered.

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][1023]INFO:SPI Alarm Not triggered.

AFE ID: 0[tiAfe79_controls.c][ti_afe79_checkDeviceHealth][1035]INFO:MCU Okay.

AFE Device Health 0x7

Any guidance on the root cause of these issues is appreciated. If there are additionaly diagnositics that would be insightful, please let us know. We have also attached our configuration file for the device.

############## Read me ##############

#In HSDC Pro DAC tab, Select AFE79xx_2x2TX_44210; Data Rate = 491.52M

#In HSDC Pro ADC tab, Select AFE79xx_2x2RX_44210; Data Rate = 491.52M ---> To capture 4 RX channels

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = True # setup FPGA (TSW14J56) using HSDC Pro

############## Top Level ##############

sysParams.FRef = 600

sysParams.FadcRx = 3000

sysParams.FadcFb = 3000

sysParams.Fdac = 12000

sysParams.externalClockRx=False

sysParams.externalClockTx=False

############## Digital Chain ##############

##### RX #####

sysParams.ddcFactorRx = [12,12,12,12] #DDC decimation factor for RX A, B, C and D

sysParams.rxNco0 = [[9500,9500], #Band0, Band1 for RXA

[9500,9500], #Band0, Band1 for RXB

[9500,9500], #Band0, Band1 for RXC

[9500,9500]] #Band0, Band1 for RXD

#sysParams.rxNco0 = [[5400,5400], #Band0, Band1 for RXA

# [5400,5400], #Band0, Band1 for RXB

# [5400,5400], #Band0, Band1 for RXC

# [5400,5400]] #Band0, Band1 for RXD

##### FB #####

sysParams.fbEnable = [False,False]

sysParams.ddcFactorFb = [12,12] #DDC decimation factor for FB 1 and 2

sysParams.fbNco0 = [9500,9500] #Band0 for FB1 and FB2

##### TX #####

sysParams.ducFactorTx = [48,48,48,48] #DUC interpolation factor for TX A, B, C and D

sysParams.txNco0 = [[9500,9500], #Band0, Band1 for TXA

[9500,9500], #Band0, Band1 for TXB

[9500,9500], #Band0, Band1 for TXC

[9500,9500]] #Band0, Band1 for TXD

#sysParams.txNco0 = [[5400,5400], #Band0, Band1 for TXA

# [5400,5400], #Band0, Band1 for TXB

# [5400,5400], #Band0, Band1 for TXC

# [5400,5400]] #Band0, Band1 for TXD

############## JESD ##############

##### ADC-JESD #####

sysParams.jesdSystemMode= [3,3]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; rx -rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb -fb- fb -fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol= [0,0] # 0 - 8b/10b encoding; 2 - 64b/66b encoding

sysParams.LMFSHdRx = ["24410","24410","24410","24410"]

# The 2nd and 4th are valid only for jesdSystemMode values in (0,2).

# For other modes, select 4 converter modes for 1st and 3rd.

sysParams.LMFSHdFb = ["22210","22210"]

sysParams.rxJesdTxScr = [True,True,True,True]

sysParams.fbJesdTxScr = [True,True]

sysParams.rxJesdTxK = [16,16,16,16]

sysParams.fbJesdTxK = [16,16]

sysParams.serdesTxLanePolarity =[0,0,0,0,0,0,0,0]

sysParams.jesdTxLaneMux = [2,3,6,7,0,1,4,5] # Enter which lanes you want in each location.

##### DAC-JESD #####

sysParams.jesdRxProtocol= [0,0]

sysParams.LMFSHdTx = ["24410","24410","24410","24410"]

sysParams.serdesRxLanePolarity = [0,0,0,0,0,0,0,0]

sysParams.jesdRxLaneMux = [4,5,0,1,6,7,2,3] # Enter which lanes you want in each location.

#sysParams.jesdRxLaneMux = [0,1,2,3,4,6,7,5] # Enter which lanes you want in each location.

sysParams.jesdRxRbd = [4, 4]

sysParams.jesdRxScr = [True,True,True,True]

sysParams.jesdRxK = [16,16,16,16]

##### JESD Common #####

sysParams.jesdABLvdsSync= False

sysParams.jesdCDLvdsSync= False

sysParams.syncLoopBack = True #JESD Sync signal is connected to FPGA

############## GPIO ##############

sysParams.gpioMapping = {

'H8': 'ADC_SYNC0',

'H7': 'DAC_SYNC0',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'ADC_SYNC1',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

############## LMK Params ##############

lmkParams.lmkVcoFreq = 3000

lmkParams.xtalFreq = 122.88

lmkParams.sysrefFreq = 3000/1024

lmkParams.pllEn = True

lmkParams.inputClk = 480 # Valid only when lmkParams.pllEn = False

lmkParams.lmkFrefClk = True

setupParams.fpgaRefClk = 125 # Should be equal to LaneRate/40 for TSW14J56

pathdz = "C:/Users/Dz/Documents/Texas Instruments/AFE79xxLatte/lib/"

#lmkParams.pllEn = False

#lmkParams.inputClk = 1000 # Valid only when lmkParams.pllEn = False

#lmkParams.lmkFrefClk = True

#setupParams.fpgaRefClk = 125 # Should be equal to LaneRate/40 for TSW14J56

############## Logging ##############

#logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.setFileName(pathdz+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x21 #Modify to 0x1 to save register scequence to log file. Script takes more time to execute.

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

#-------------------------------------------------------------------------------------------------#

#added by dz

#PhaseOffset=int(90/(360/2^16))

#PhaseOffset=int(32768)

#device.writeReg(0x12,0x2)

#device.writeReg(0xE1,(PhaseOffset>>8)&0xFF)

#device.writeReg(0xE0,PhaseOffset&0xFF)

#device.writeReg(0x12,0x0)

lmklogDumpInst=mLogDump.logDump(pathdz+r"\Afe79xxPg1_LMK.txt")

lmklogDumpInst.logFormat=0x21

lmk.logClassInst = lmklogDumpInst

lmk.rawWriteLogEn=1

setupParams.skipLmk = False

AFE.initializeConfig()

lmkParams.sysrefFreq = AFE.systemStatus.sysrefFreq

lmkParams.lmkPulseSysrefMode = False

AFE.LMK.lmkConfig()