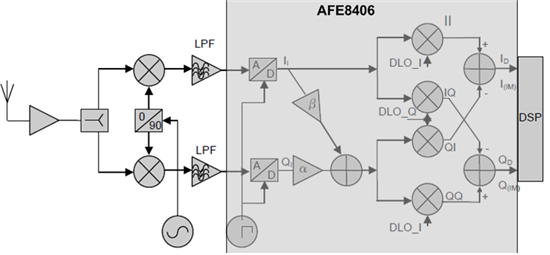

Hello! I would use chip AE8406 as a multi-carrier receiver "digital low IF Weaver architecture" (see illustration). That is planned to use the chip in the "UMTS complex".

Questions:

- Do I understand, that AFE8406 DDC mixer - complex mixer (as I have quoted above figure)

- Is it possible to somehow compensate for the imbalance within the chip amplitude and phase I and Q quadrature I emerged after the analog mixer (with gains α and β to modify the I and Q signals)? Is it possible for this purpose to use the internal RAGC (though given that the external control amplifier connected to the AFE8406 with DVGA not in sight).

- is it possible to use RAGC Fixed gain of each of the quadrature