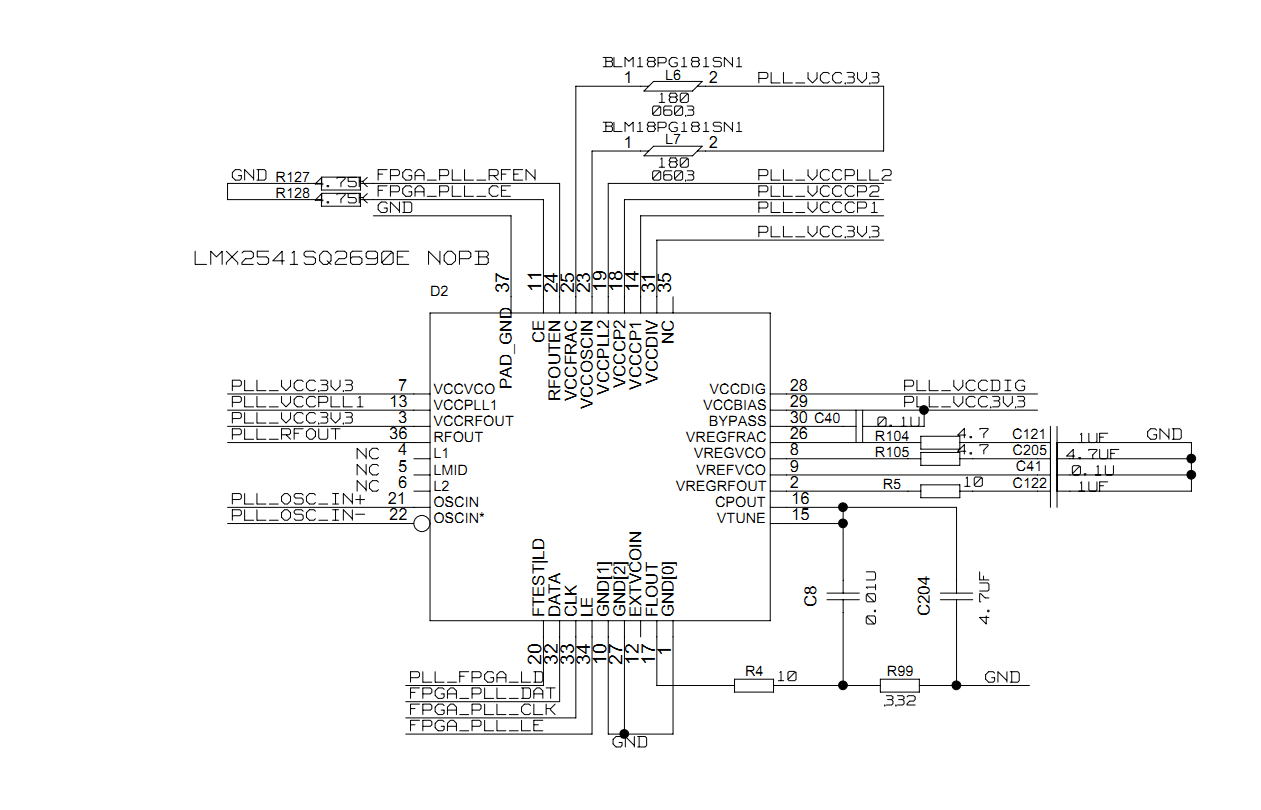

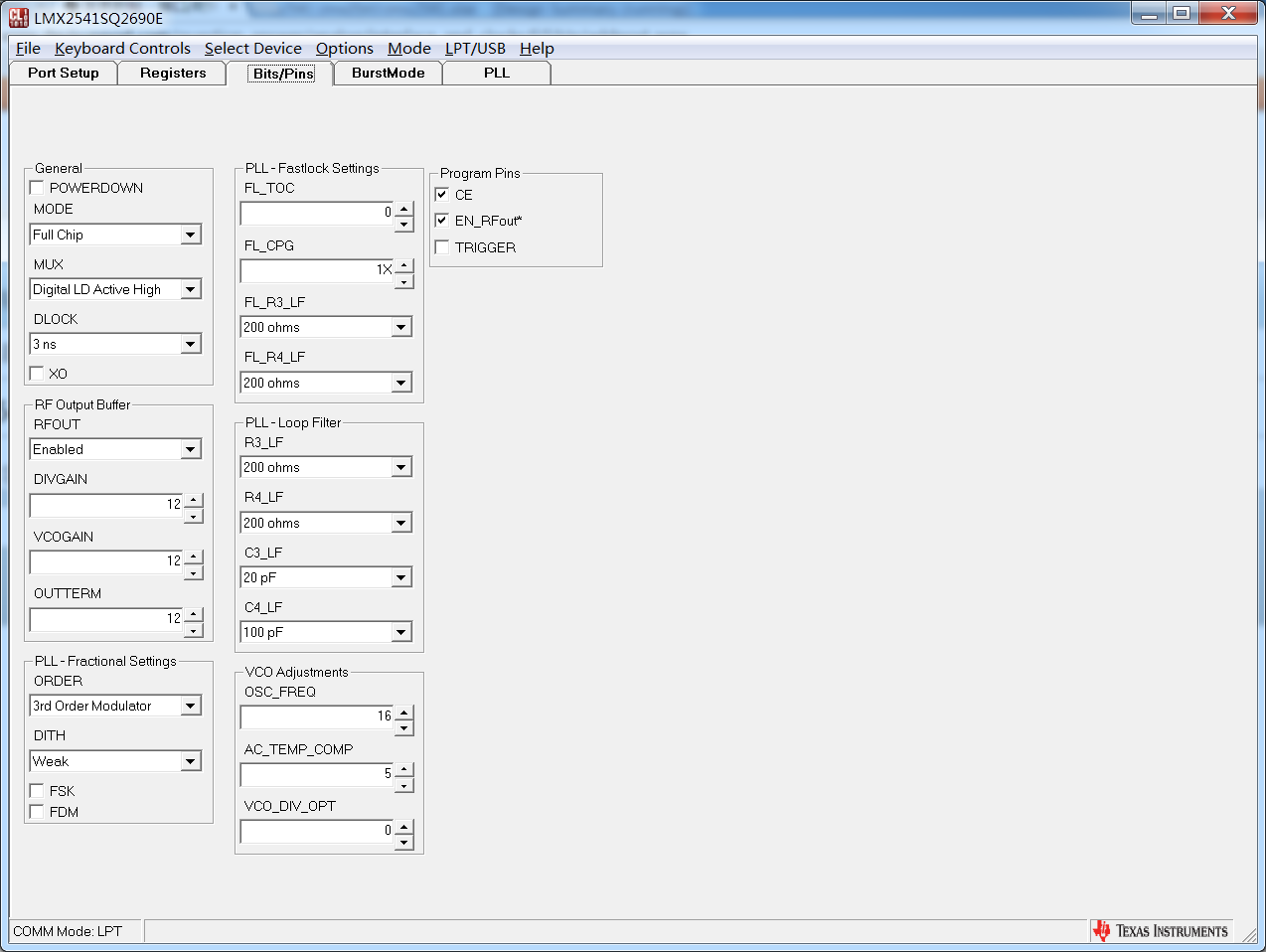

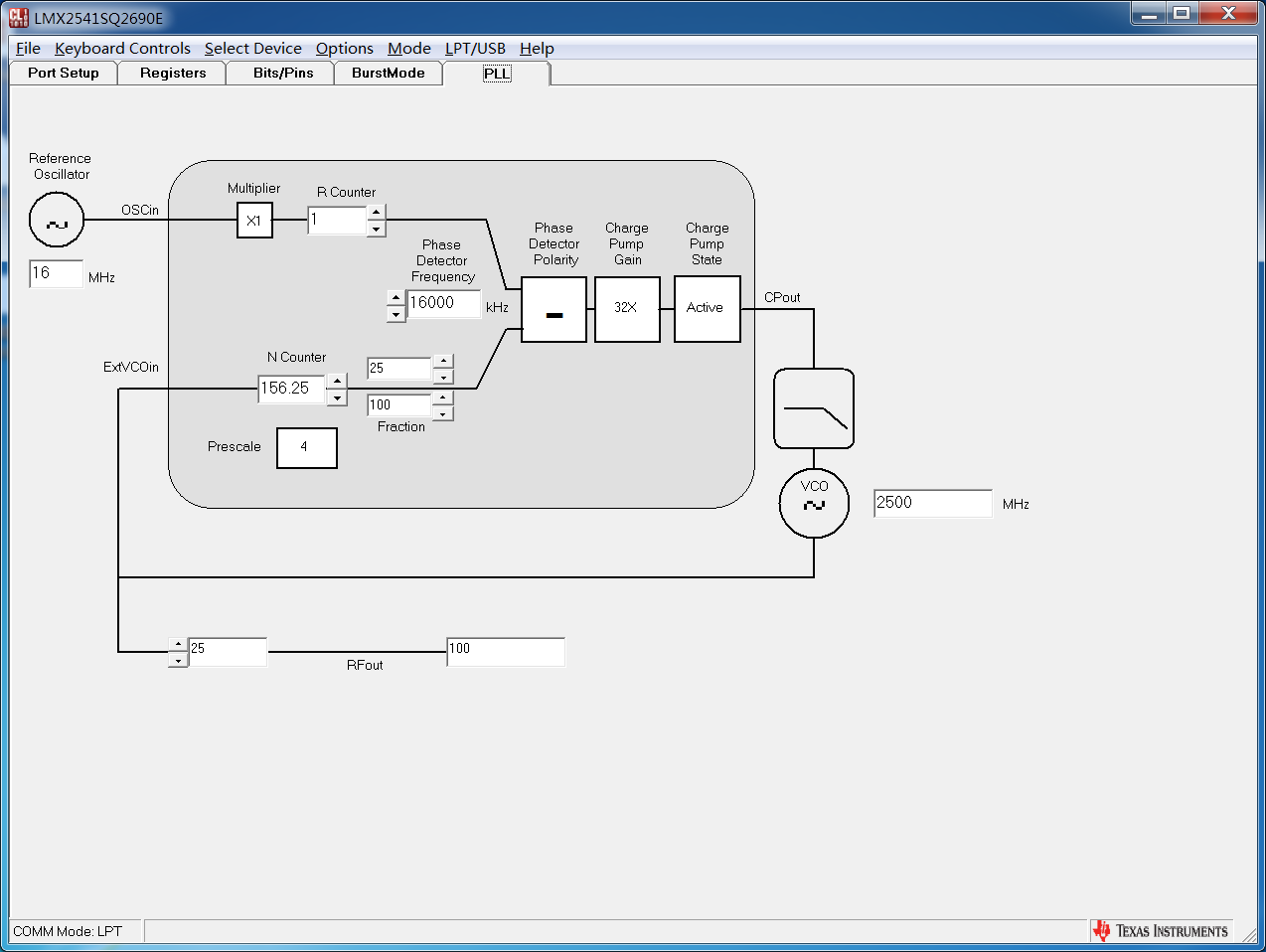

hello, i use the FPGA to configure this chip , the input frequcecy is 16MHz. I try to generate 100Mhz output frequcecy.But the output frequcecy is not right , about +2 to +5MHz more.these are my configuration designed from codeloader .

R7 0x00000017

R13 0x0000008D

R12 0x0000001C

R9 0x28001409

R8 0x0111CE58

R6 0x001F3326

R5 0xA0000005

R4 0x88019104

R3 0x00307F03

R2 0x04000642

R1 0x00000011

R0 0x001909C0

when i change the value of C3 and C4,the output frequency differ,but not my desired frequency. And the LD state is always unlocked(low).

Is there anything wrong about the configuration above?

regard

josh