Hello Team,

I have a customer having trouble bringing up the AFE7769EVM. Can you please take a look at the following and provide your feedback.

I installed AFE7769EVM and TSW14J56 software and GUI, applied 10MHz clock (0dBm signal level, please let me know what the signal level should be) to LMK CLK IN (also, please let me know if 10MHz should be applied to LMK CLK IN) and followed the steps in section 4 of “AFE77xxEVM User's Guide” document.

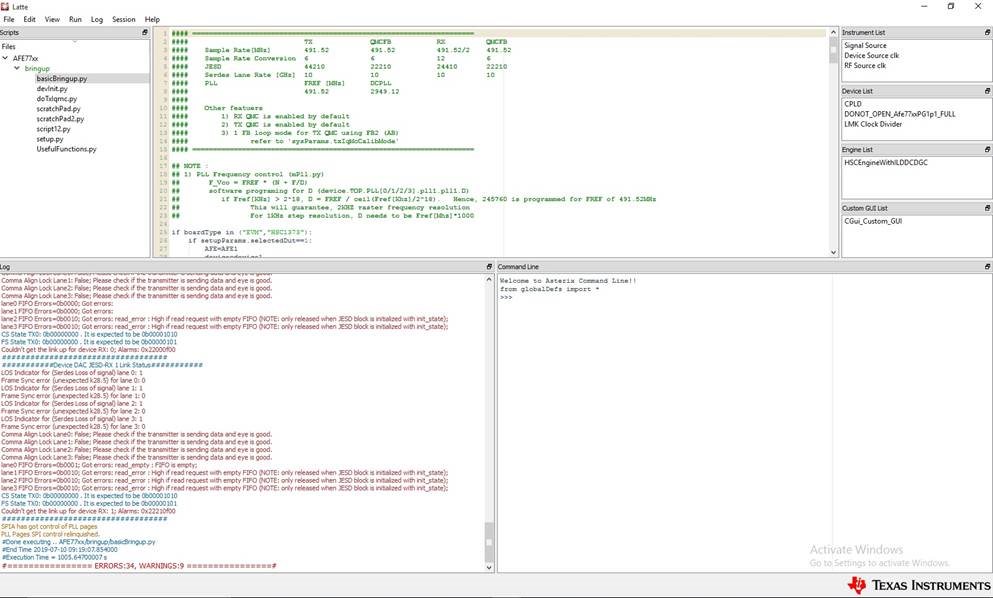

Up to section 4.4, everything looks good. However, after running basicBringup.py the following errors and warnings were reported. I ran the basicBringup.py for the second time as mentioned in the document and got same errors and warnings. The log files for both tries are attached.

Could you please review the log files and let me know why these errors and warnings are reported?

Please note that after running the basicBringup.py the AFE7769EVM board draws around 2.6A that is close to what is mentioned in the 4.4 section.

#====== #Executing .. AFE77xx/bringup/setup.py #Start Time 2019-07-10 08:41:59.609000 AFE77xxLibraryPG1P1 Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. #Done executing .. AFE77xx/bringup/setup.py #End Time 2019-07-10 08:42:05.259000 #Execution Time = 5.65000009537 s #================ ERRORS:0, WARNINGS:0 ================# #====== #Executing .. AFE77xx/bringup/devInit.py #Start Time 2019-07-10 08:42:30.039000 CPLD - No Capture Device defined CPLD - Reset property was not found DONOT_OPEN_Afe77xxPG1p1_FULL - No Capture Device defined DONOT_OPEN_Afe77xxPG1p1_FULL - Reset property was not found LMK Clock Divider - No Capture Device defined LMK Clock Divider - Reset property was not found Error making connections. Check if all state variables exist for makeConnections method in HSC Engine Successfully Loaded the Libraries. Unable to access the object myfpga.head.page.Common.Lanes._Lanes_in_use Unable to access the object myfpga.head.page.Common.Lanes._Lane_sel Unable to access the object myfpga.head.page.Common.Final_Options._Stream Unable to access the object myfpga.head.page.Common.Final_Options._pack_mode Unable to access the object myfpga.head.page.Common.Final_Options._mode_24bit Unable to access the object myfpga.head.page.Common.Final_Options._samp_drop 12549 #Done executing .. AFE77xx/bringup/devInit.py #End Time 2019-07-10 08:43:07.606000 #Execution Time = 37.5669999123 s #================ ERRORS:7, WARNINGS:6 ================# #====== #Executing .. AFE77xx/bringup/basicBringup.py #Start Time 2019-07-10 08:43:50.362000 DONOT_OPEN_Afe77xxPG1p1_FULL - Device registers reset. DONOT_OPEN_Afe77xxPG1p1_FULL - Reset property was not found. Use setResetProperty() to fix this. chipType: 0xa chipId: 0x77 chipVersion: 0x11 2T2R1F Number: 0 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 2T2R1F Number: 1 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 11.52 2048.0 LMK Clock Divider - Device registers reset. LMK Clock Divider - Device registers reset. Fuse farm load autoload done successful No autload error MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False SPIA has got control of PLL pages pll0: True; LO Frequency: 3500.0 pll1: True; LO Frequency: 2949.12 PLL Pages SPI control relinquished. FB DSA 3.5G Band *TX IQMC Patch Apply* SPIA has got control of PLL pages PLL Pages SPI control relinquished. FW_VERSION=0x11119e MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False attack_value: 2899.74593284 decay_value: 1630.64697059 attack_value: 2899.74593284 decay_value: 1630.64697059 SPIA has got control of PLL pages PLL Pages SPI control relinquished. Sysref to RX AB, Read: 3; expected: 3 Sysref to RX CD, Read: 3; expected: 3 Sysref to FB A, Read: 1; expected: 1 Sysref to FB D, Read: 1; expected: 1 Sysref to TX AB, Read: 7; expected: 7 Sysref to TX CD, Read: 7; expected: 7 Digital Clock, Read: True; expected: 1 Sysref to Digital, Read: True; expected: 1 Sysref to Analog, Read: 7; expected: 7 Sysref Read as expected ###########Device DAC JESD-RX 0 Link Status########### LOS Indicator for (Serdes Loss of signal) lane 0: 1 Frame Sync error (unexpected k28.5) for lane 0: 0 LOS Indicator for (Serdes Loss of signal) lane 1: 1 Frame Sync error (unexpected k28.5) for lane 1: 0 LOS Indicator for (Serdes Loss of signal) lane 2: 1 Frame Sync error (unexpected k28.5) for lane 2: 0 LOS Indicator for (Serdes Loss of signal) lane 3: 1 Frame Sync error (unexpected k28.5) for lane 3: 0 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b00001010 FS State TX0: 0b00000000 . It is expected to be 0b00000101 Couldn't get the link up for device RX: 0; Alarms: 0xf00 ################################### ###########Device DAC JESD-RX 1 Link Status########### LOS Indicator for (Serdes Loss of signal) lane 0: 1 Frame Sync error (unexpected k28.5) for lane 0: 0 LOS Indicator for (Serdes Loss of signal) lane 1: 1 Frame Sync error (unexpected k28.5) for lane 1: 0 LOS Indicator for (Serdes Loss of signal) lane 2: 1 Frame Sync error (unexpected k28.5) for lane 2: 0 LOS Indicator for (Serdes Loss of signal) lane 3: 1 Frame Sync error (unexpected k28.5) for lane 3: 0 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. lane0 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane2 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane3 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); CS State TX0: 0b00000000 . It is expected to be 0b00001010 FS State TX0: 0b00000000 . It is expected to be 0b00000101 Couldn't get the link up for device RX: 1; Alarms: 0x22220f00 ################################### SPIA has got control of PLL pages PLL Pages SPI control relinquished. #Done executing .. AFE77xx/bringup/basicBringup.py #End Time 2019-07-10 09:00:39.221000 #Execution Time = 1008.85899997 s #================ ERRORS:30, WARNINGS:9 ================#

#====== #Executing .. AFE77xx/bringup/setup.py #Start Time 2019-07-10 08:41:59.609000 AFE77xxLibraryPG1P1 Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. #Done executing .. AFE77xx/bringup/setup.py #End Time 2019-07-10 08:42:05.259000 #Execution Time = 5.65000009537 s #================ ERRORS:0, WARNINGS:0 ================# #====== #Executing .. AFE77xx/bringup/devInit.py #Start Time 2019-07-10 08:42:30.039000 CPLD - No Capture Device defined CPLD - Reset property was not found DONOT_OPEN_Afe77xxPG1p1_FULL - No Capture Device defined DONOT_OPEN_Afe77xxPG1p1_FULL - Reset property was not found LMK Clock Divider - No Capture Device defined LMK Clock Divider - Reset property was not found Error making connections. Check if all state variables exist for makeConnections method in HSC Engine Successfully Loaded the Libraries. Unable to access the object myfpga.head.page.Common.Lanes._Lanes_in_use Unable to access the object myfpga.head.page.Common.Lanes._Lane_sel Unable to access the object myfpga.head.page.Common.Final_Options._Stream Unable to access the object myfpga.head.page.Common.Final_Options._pack_mode Unable to access the object myfpga.head.page.Common.Final_Options._mode_24bit Unable to access the object myfpga.head.page.Common.Final_Options._samp_drop 12549 #Done executing .. AFE77xx/bringup/devInit.py #End Time 2019-07-10 08:43:07.606000 #Execution Time = 37.5669999123 s #================ ERRORS:7, WARNINGS:6 ================# #====== #Executing .. AFE77xx/bringup/basicBringup.py #Start Time 2019-07-10 08:43:50.362000 DONOT_OPEN_Afe77xxPG1p1_FULL - Device registers reset. DONOT_OPEN_Afe77xxPG1p1_FULL - Reset property was not found. Use setResetProperty() to fix this. chipType: 0xa chipId: 0x77 chipVersion: 0x11 2T2R1F Number: 0 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 2T2R1F Number: 1 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 11.52 2048.0 LMK Clock Divider - Device registers reset. LMK Clock Divider - Device registers reset. Fuse farm load autoload done successful No autload error MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False SPIA has got control of PLL pages pll0: True; LO Frequency: 3500.0 pll1: True; LO Frequency: 2949.12 PLL Pages SPI control relinquished. FB DSA 3.5G Band *TX IQMC Patch Apply* SPIA has got control of PLL pages PLL Pages SPI control relinquished. FW_VERSION=0x11119e MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False attack_value: 2899.74593284 decay_value: 1630.64697059 attack_value: 2899.74593284 decay_value: 1630.64697059 SPIA has got control of PLL pages PLL Pages SPI control relinquished. Sysref to RX AB, Read: 3; expected: 3 Sysref to RX CD, Read: 3; expected: 3 Sysref to FB A, Read: 1; expected: 1 Sysref to FB D, Read: 1; expected: 1 Sysref to TX AB, Read: 7; expected: 7 Sysref to TX CD, Read: 7; expected: 7 Digital Clock, Read: True; expected: 1 Sysref to Digital, Read: True; expected: 1 Sysref to Analog, Read: 7; expected: 7 Sysref Read as expected ###########Device DAC JESD-RX 0 Link Status########### LOS Indicator for (Serdes Loss of signal) lane 0: 1 Frame Sync error (unexpected k28.5) for lane 0: 0 LOS Indicator for (Serdes Loss of signal) lane 1: 1 Frame Sync error (unexpected k28.5) for lane 1: 0 LOS Indicator for (Serdes Loss of signal) lane 2: 1 Frame Sync error (unexpected k28.5) for lane 2: 0 LOS Indicator for (Serdes Loss of signal) lane 3: 1 Frame Sync error (unexpected k28.5) for lane 3: 0 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b00001010 FS State TX0: 0b00000000 . It is expected to be 0b00000101 Couldn't get the link up for device RX: 0; Alarms: 0xf00 ################################### ###########Device DAC JESD-RX 1 Link Status########### LOS Indicator for (Serdes Loss of signal) lane 0: 1 Frame Sync error (unexpected k28.5) for lane 0: 0 LOS Indicator for (Serdes Loss of signal) lane 1: 1 Frame Sync error (unexpected k28.5) for lane 1: 0 LOS Indicator for (Serdes Loss of signal) lane 2: 1 Frame Sync error (unexpected k28.5) for lane 2: 0 LOS Indicator for (Serdes Loss of signal) lane 3: 1 Frame Sync error (unexpected k28.5) for lane 3: 0 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. lane0 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane2 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane3 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); CS State TX0: 0b00000000 . It is expected to be 0b00001010 FS State TX0: 0b00000000 . It is expected to be 0b00000101 Couldn't get the link up for device RX: 1; Alarms: 0x22220f00 ################################### SPIA has got control of PLL pages PLL Pages SPI control relinquished. #Done executing .. AFE77xx/bringup/basicBringup.py #End Time 2019-07-10 09:00:39.221000 #Execution Time = 1008.85899997 s #================ ERRORS:30, WARNINGS:9 ================# #====== #Executing .. AFE77xx/bringup/basicBringup.py #Start Time 2019-07-10 09:02:22.207000 DONOT_OPEN_Afe77xxPG1p1_FULL - Device registers reset. DONOT_OPEN_Afe77xxPG1p1_FULL - Reset property was not found. Use setResetProperty() to fix this. chipType: 0xa chipId: 0x77 chipVersion: 0x11 2T2R1F Number: 0 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 2T2R1F Number: 1 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 11.52 2048.0 LMK Clock Divider - Device registers reset. LMK Clock Divider - Device registers reset. Fuse farm load autoload done successful No autload error MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False SPIA has got control of PLL pages pll0: True; LO Frequency: 3500.0 pll1: True; LO Frequency: 2949.12 PLL Pages SPI control relinquished. FB DSA 3.5G Band *TX IQMC Patch Apply* SPIA has got control of PLL pages PLL Pages SPI control relinquished. FW_VERSION=0x11119e MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False MACRO_READY: True MACRO_ACK: True MACRO_DONE: True MACRO_ERROR: False attack_value: 2899.74593284 decay_value: 1630.64697059 attack_value: 2899.74593284 decay_value: 1630.64697059 SPIA has got control of PLL pages PLL Pages SPI control relinquished. Sysref to RX AB, Read: 3; expected: 3 Sysref to RX CD, Read: 3; expected: 3 Sysref to FB A, Read: 1; expected: 1 Sysref to FB D, Read: 1; expected: 1 Sysref to TX AB, Read: 7; expected: 7 Sysref to TX CD, Read: 7; expected: 7 Digital Clock, Read: True; expected: 1 Sysref to Digital, Read: True; expected: 1 Sysref to Analog, Read: 7; expected: 7 Sysref Read as expected ###########Device DAC JESD-RX 0 Link Status########### LOS Indicator for (Serdes Loss of signal) lane 0: 1 Frame Sync error (unexpected k28.5) for lane 0: 0 LOS Indicator for (Serdes Loss of signal) lane 1: 1 Frame Sync error (unexpected k28.5) for lane 1: 0 LOS Indicator for (Serdes Loss of signal) lane 2: 1 Frame Sync error (unexpected k28.5) for lane 2: 0 LOS Indicator for (Serdes Loss of signal) lane 3: 1 Frame Sync error (unexpected k28.5) for lane 3: 0 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. lane0 FIFO Errors=0b0000; Got errors: lane1 FIFO Errors=0b0000; Got errors: lane2 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane3 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); CS State TX0: 0b00000000 . It is expected to be 0b00001010 FS State TX0: 0b00000000 . It is expected to be 0b00000101 Couldn't get the link up for device RX: 0; Alarms: 0x22000f00 ################################### ###########Device DAC JESD-RX 1 Link Status########### LOS Indicator for (Serdes Loss of signal) lane 0: 1 Frame Sync error (unexpected k28.5) for lane 0: 0 LOS Indicator for (Serdes Loss of signal) lane 1: 1 Frame Sync error (unexpected k28.5) for lane 1: 0 LOS Indicator for (Serdes Loss of signal) lane 2: 1 Frame Sync error (unexpected k28.5) for lane 2: 0 LOS Indicator for (Serdes Loss of signal) lane 3: 1 Frame Sync error (unexpected k28.5) for lane 3: 0 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. lane0 FIFO Errors=0b0001; Got errors: read_empty : FIFO is empty; lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane2 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); lane3 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state); CS State TX0: 0b00000000 . It is expected to be 0b00001010 FS State TX0: 0b00000000 . It is expected to be 0b00000101 Couldn't get the link up for device RX: 1; Alarms: 0x22210f00 ################################### SPIA has got control of PLL pages PLL Pages SPI control relinquished. #Done executing .. AFE77xx/bringup/basicBringup.py #End Time 2019-07-10 09:19:07.854000 #Execution Time = 1005.64700007 s #================ ERRORS:34, WARNINGS:9 ================#