Dear experts,

I referred the ticket of https://e2e.ti.com/support/tools/code-composer-studio-group/ccs/f/code-composer-studio-forum/835932/ccs-awr1642boost-awr1642-watchdog-function-to-achieve/3091964#3091964 to implement the Watchdog feature.

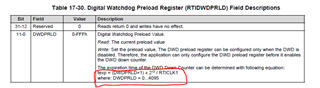

The document describes that the range of preload values is between 0 ~ 0xFFF., which means the maximum time expiration is 167.7 ms.

Q1. May I know the RTICLK1 is 200 MHz (fixed value?)?

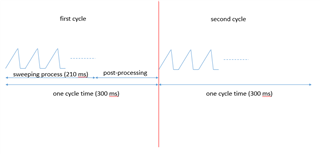

Q2. How to implement the Watchdog if cycle time is larger than 167.7 ms?

Sincerely,

Jack