Other Parts Discussed in Thread: MMWCAS-RF-EVM, TDA2

Hello,

We have designed an Imaging Radar Platform based on AWR2243. Data is transferred over LVDS from the chips. CRC calculated on the chip and on the final destination are matched, so we are confident that the data from ADC is received correctly.

We are testing now various configurations but have a issue with sampled received signal.

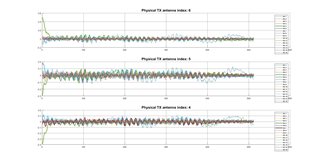

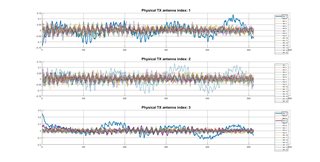

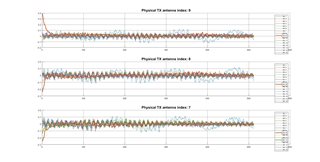

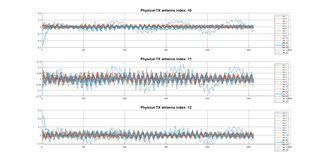

We are using TDM mode with 12 Tx and 16Rx. The issue we are facing is next:

- If master chip is transmitting, no matter Tx1, Tx2 or Tx3, the received signal from his Rx antenna is having strange behavior in first around 10 samples. The other 12 Rx from slave chips have values as expected

- When any of the slave chips is transmitting, again no matter which antenna, only the receive antennas from the chip that is receiving are corrupted in the same manner as above

- It is always only one Tx antenna on, but the same problem on receive antennas is seen only on the chip that is transmitting

- On above pictures Tx antenna index 1 represents first transmit antenna of master chip and antenna index 12 third antenna of fourth chip

- On above pictures Rx antenna index 1 represents first receive antenna of master chip and antenna index 16 fourth antenna of fourth chip

- Chips are positioned same as on mmWCAS-RF-EVM.

We suspected a problem with power supply but looking at oscilloscope all 3V3, 1V8, 1V2 and 1V0 look inside tolerance.

Changing ADC start time, TX start time, Fs, slope or TX backoff provides no improvements.

Do you have any advice how to proceed?