Hello, I am following the procedure given in the thread: AWR2243BOOST: mmwave Device Power on failed for deviceMap1 with error -8 in AWR Single Chip setup with Jetson AGX - Sensors forum - Sensors - TI E2E support forums.

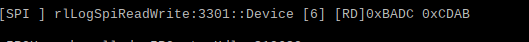

I am able to get to step 7 where HOSTIRQ is brought low and my host device begins reading the message from the AWR. Here is a wave form capture of just that:

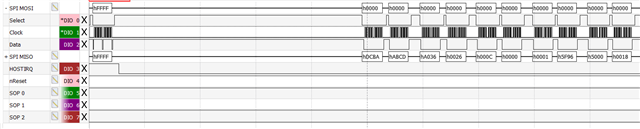

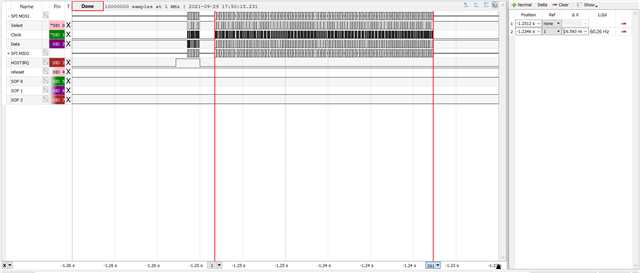

This string of message on MISO goes on for roughly 16 ms, shown here:

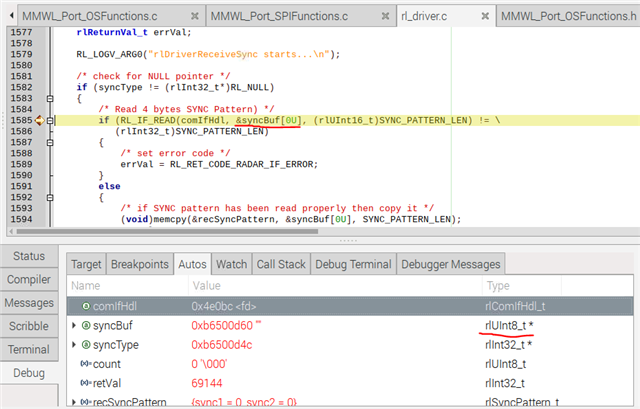

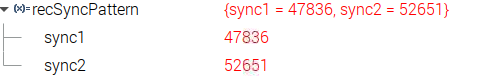

I have also discovered that rlDriverRecieveSync results in the count reaching the sync scan threshold (rl_driver.c line 1628).

Any advice on how to proceed or why the count reaches this threshold?

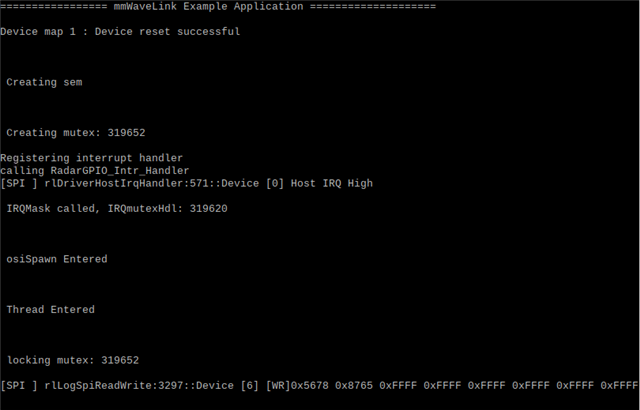

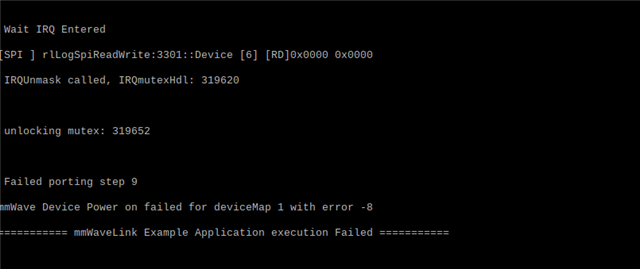

For completeness here is my terminal window after executing the application: