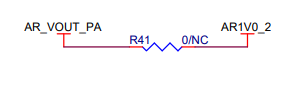

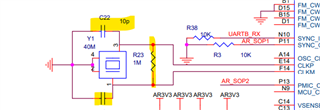

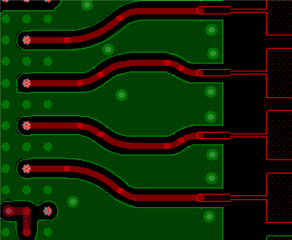

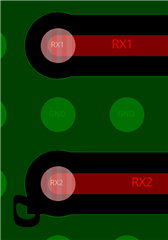

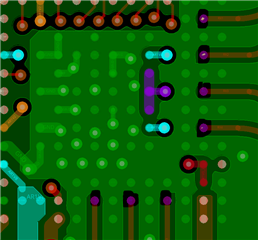

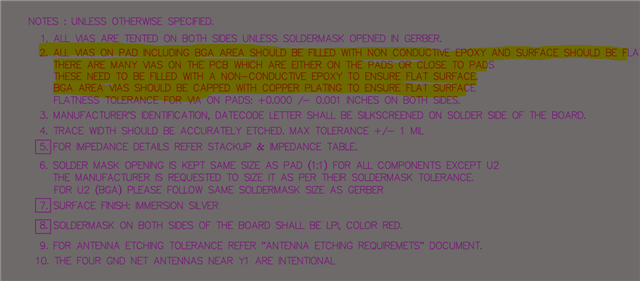

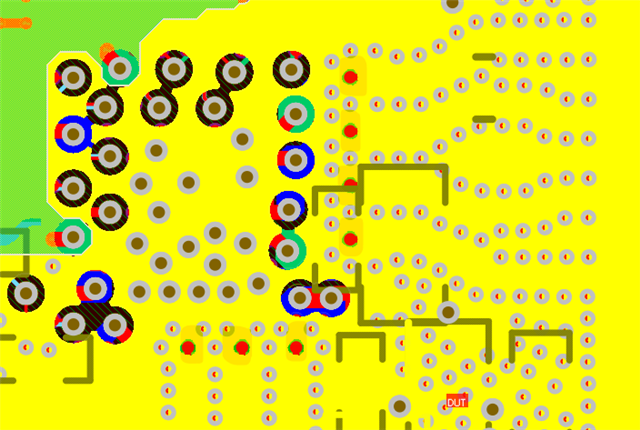

Hardware: PCB designed by ourselves with IWR1443 reference to IWR1443Boost.

Software: xwr14xx_mmw_demo.bin + mmwave demo visualizer 2.1.

Test environment: IWR1443 board face to the ceiling, about 2.5 meters.

Everything works fine.

IWR1443Boost can get about 113dB at 2.5 meters, but our PCB board can only get 90dB.

Please check our PCB files by Cadence 16.6 and give us some advices.