Other Parts Discussed in Thread: PGA460

- When I try to read the distance, I occasionally get a “device busy” diagnostic message.

- The issue happens sometimes after 5s but that time can be a lot longer. When the issue happens, I get either 1 or 2 of those “device busy” messages shorty after one another.

- The issue seems to be completely random.

Technically this is about the diagnostics byte which should by 0x40. When the problem occurs, I get 0x4B (0b0100’1011) instead:

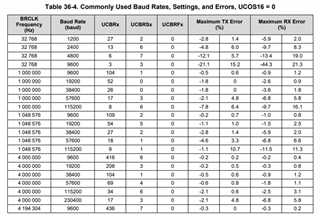

I don’t know how to interpret the value 0x4B. It tells me that the device is busy but at the same time it tells me that the baud rate is too high (which it isn’t – I am using 57600) and also that the checksum from the master is wrong (which is not possible because I use the exact same code every time I initiate a read).

The sequence is as follows:

- Do the initialisation

- Loop:

- Wait 100ms

- Send command 0x00: Burst and listen (Preset1)

- Wait 500ms

- Send command 0x05: Ultrasonic measurement result

- Read response à This is where I occasionally get diagnostic code 0x4B instead of 0x40

- Back to a.)

What I want to know is quite simply what diagnostic code 0x4B really means. Is the device busy or is it a sync field issue or is it a checksum issue? If the device is busy – why is it busy considering above very defensive timing.