Other Parts Discussed in Thread: TMP102

Hi Team,

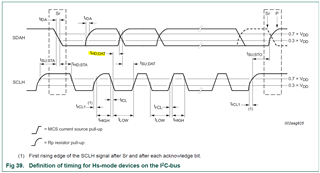

When my customer measureing I2C AC Timing at 630k Hz HS Mode, they get data hold time(tHD;DAT) ~= 500ns.

It will over the tHD;DAT Max of TMP103.

Could you help check:

1. Is this timing acceptable and will it not cause any issue?

2. Theoretically, the hold time should be as large as possible. Is it possible to relax the spec to tHD; DAT Max = ∞ ?

Looking forward to your feedback.

Thanks and Best regards,

Jamie