Hi team,

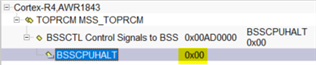

how can dedicated that the BSS is on halt? It looks like the BSS halts and unhalts correctly (power wise), but how we can otherwise verify it? The Debugger showing 0x00 (pls. see screenshot below) which was not expected based on the TRM guidance. Why are bits 16-23 set to 0xAD but the bits 24-31 (for BSSCPUHALT field) are not?

Power wise we can see a different between halt and unhalt. Furthermore, why is the BSSCPUHALT register not set to 0xAD in the SOC_haltBSS function?

Thanks and best regards

Jens