Hello,

We have created 10 sections in TCMB RAM 4bytes each .

| Section | Start address | Length in bytes | Model for compilation |

| 1 | 0x8002A00 | 4 | ROM_MODEL |

| 2 | 0x8002A04 | 4 | ROM_MODEL |

| 3 | 0x8002A08 | 4 | ROM_MODEL |

| 4 | 0x8002A0C | 4 | ROM_MODEL |

| 5 | 0x8002A10 | 4 | ROM_MODEL |

| 6 |

0x8002A14 |

4 | RAM_MODEL |

| 7 | 0x8002A18 | 4 | RAM_MODEL |

| 8 | 0x800 2A1C | 4 | RAM_MODEL |

| 9 | 0x800 2A20 | 4 | RAM_MODEL |

| 10 | 0x800 2A24 | 4 | RAM_MODEL |

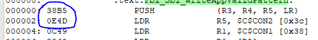

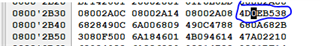

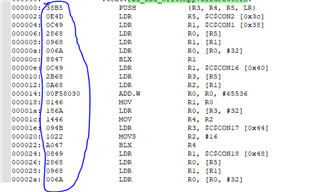

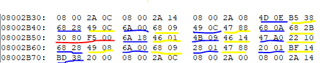

We generate 2 hex files , Hex file one has sections 1 to 5 and Hex file two has section 6 to 10 .when we place them on ram ,Section 1 to 5 are placed in little endian and section 6 to 10 are placed in big endian .

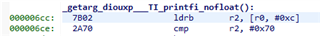

(We use ROM model for compiling Hex file one and RAM model for compiling Hex file two , please refer attached image for reference how they placed in ram memory , this image is captured during debugging .

Compiler used : T_ti arm V18.12.2 )

WE EXPECT SECTION 6 TO 10 SHOULD ALSO BE PLACED IN LITTLE ENDIAN . Could you please provide us a solution or comment on what we are doing wrong.