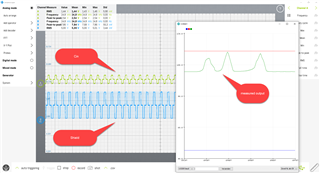

Hello, below in the image is the excitation signal waveform measured on the Cin pin from the FDC1004.

There are a couple of questions:

1). why is the Cin/excitation signal shaped like this (in 2 steps)?

2). are the Cin and excitation signals driven from the same generator or are there 2 generators inside the chip?

3). what is the bandwith of the signal? Or the delta-t of the rising flank of the signal / rising time?

Thanks!