Other Parts Discussed in Thread: AWR1243, AWR2243

I am looking at implementing the SPI initialization sequence using the API document and have issue understanding the material provided.

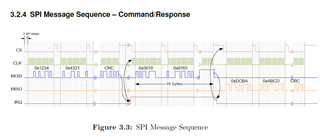

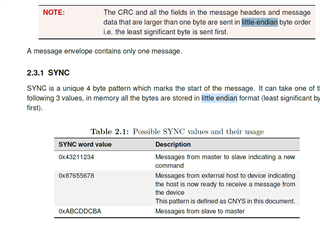

The example shows Big Endian on the sync word but the document also calls for

Which of the above 2 holds true?

Also how critical is the delay between the CS and CLK as you mention 2 clock cycles. Our host mcu has a little over 1 Clock cycle but less than 2. Does that pose an issue.

Kindly advise.

Shyam