Hello,

We need to measure a LVDT attached to a hydraulic servo valve and I am not sure what are the proper way to design the excitation and the whole chain conversion.

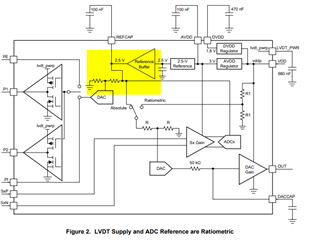

We have one MCU C2000 connected to the SPI to access all the internal registers and the analog output of the PGA is connected to one ADC input. We just need to read 0-V to 5-V Absolute Output.

The characteristics of the LVDT are as below:

- 3V RMS gives 8.5V pk-pk, what value should we choose for VDD?

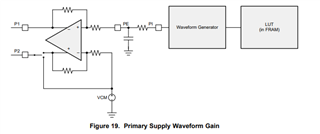

- Is it better to keep VDD regulated at 14V using the N-Channel MOSFET, then for the excitation of the LVDT configure correctly the DAC gain (Primary Supply Waveform Gain)+ external amplifier so the EXC signal is in the range 0 - 3V RMS

- Or change VDD to a lower value to get more DAC resolution?

- What is the initial range voltage of the waveform generator, before the GAIN?

- The next step would be to choose the right external resistor divider, filter then GAIN S1,S2 and S3 to have an input range of 2.5V? Is it possible to simulated the whole conversion chain?

- In the LVDT datasheet, it says Summed Output Voltage 1.26V/Vin, does it means the transformation ratio is 1.26?

- Schematic PGA970.pdf