Hi TI experts,

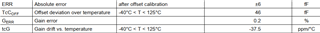

1、About the ERR,the test conditions: after offset calibration,may I ask whether this bias calibration is conducted through CIN open circuit calibration?

2、How to understand Gain error and Gain drift?Can you give an example of how they affect my measurements?

Best wishes.

Jiang