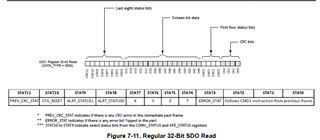

From the datasheet, figure 7-11 overviews the return data status registers. "Stat10-4 are select status bits from the CON_STATUS and AFE_STATUS registers"...

Is ALRT_STATUS1/0 = ALRT_STATUS from the CONV_STATUS register?

What are "X" to "T" status bits? Are those TEMP_STAT ... XHS_STAT bits from AFE_STATUS? Are those T ... X bits from the CON_STATUS register?

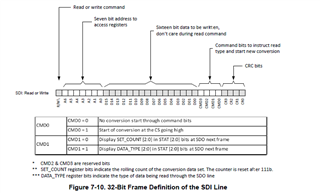

What does "CMD0 = 0, No conversion start through command bits" mean? Does that mean that sending a write command does not trigger a conversion?

What does "CMD1 =1, Start of Conversion at the CS going high" mean? Does that mean that at the end of an SPI communication operation, a conversion is triggered?