Hi,we have few questions on TMAG5170.

To understand whether SPI communication with TMAG5170 is working fine,following minimal application is sufficient on top of test code.

Tmag_init()

{

//TMAG5170startup();

/*device config initialization*/

//writeToRegister(0,0,41);

/*Sensor init*/

//writeToRegister(1,0,10);

/*System init*/

//writeToRegister(2,0,99);

/*Sensor is set up to meet above configuration with renesas micro.

* sensor in continuous active mode and interested in

only angle measurement

*/

}

Tmag_Cyclic()

{

/*

writeToRegister(0x13,0);

}

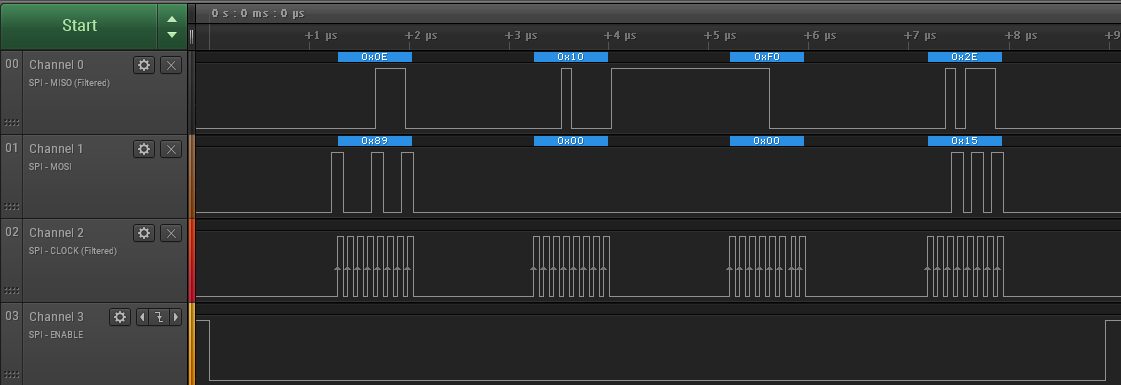

Q1:Can we ignore every write(device/sensor/system)registers of init and

read angle register periodically to see spi is fine? i.e we pass

writeToRegister(0x13,0) and after crc calculation and read bit final value

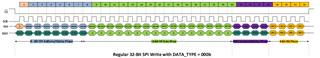

sent is (0x93,0x00,0x00,0x0f) (or) minimum write of system config(0x02,0x00,0x00,crc)needed.

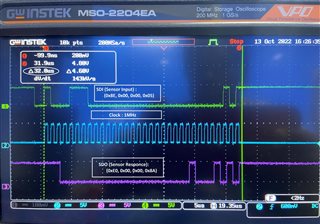

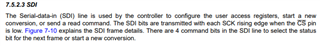

Q2:Test code indicates push one byte and read rx byte.Isn't it necessary to send complete (0x93,0x00,0x00,0x0f) and then after TMAG

checks the frame crc and responds with 32 bit response ,micro initiates read.

Q3:How to understand rx frame. we are sending(CMD0 =0,CMD1=0).Are STAT bits included even for above command.

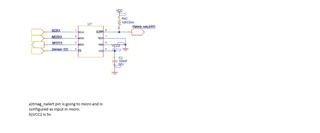

Q4:We are interfacing TMAG with rh850fl1 micro.In read register(miso) of spi channel (16 bit data can be stored)and interested in

angle measurement(magnet,spi,actual device/system/sensor configurations are ready).we want to see SPI data formats are correct and then

proceed with sending actual configuration(continuos active conversion mode..etc)

so what could be proper way to send command.send 0x93 ,0x00 and then read miso response and send 0x00,0x0f read miso response?

Thank You,

P Tulasi Krishna.