Hi,

My customer is considering using the adv frame and dynamic reconfiguration. Below notes and time diagram confuse me a lot. Need your help clarify, look forward to your comments soon, appreciated.

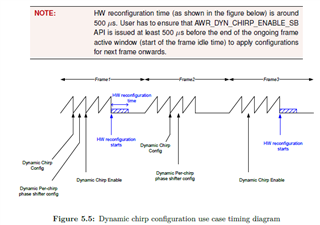

- My understanding that dynamic chirp/PS config can be called at any time as the configuration is stored in SW RAM and not applied until DYN_CHIRP_ENABLE is called, how to understand “Note that the configuration should be received by the firmware 10 ms before the end of the current frame.” Does it mean that the update configuration need at least 10ms to take effect after DYN_CHIRP_ENABLE is issued?

- How to understand the “HW reconfiguration time is around 500 us”? why it is need to issue before end of the ongoing frame active window? Can it be issued during frame idle time?

// AWR_DYN_CHIRP_ENABLE_SB

* @note 1: User needs to invoke this API within inter-frame idle time, not at boundary of frame

* end. Since dynamic chirps are configured at run time, there is not error checks done

* on the input data. If input data is out of range or invalid, device might misbehave.

* @note 2: HW reconfiguration time is around 500 us. User has to ensure that

* AWR_DYN_CHIRP_ENABLE_SB API is issued at least 500 us before the end of the ongoing

* frame active window (start of the frame idle time) to apply configurations for next

* frame onwards. \n

// AWR_DYN_PERCHIRP_PHASESHIFTER_CONF_SET_SB

* This API can be used to dynamically change the per-chirp phase shifter configuration while

* frames are on-going. The configuration will be stored in software and the new configuration

* will be applied at the end of the on-going frame. Note that the configuration should be

* received by the firmware 10 ms before the end of the current frame.