Hi,

Based on the AWR6843 Datasheet (Serial No: SWRS248D), we have differential LVDS Data Lanes, Clock lane and Frame clock lane.

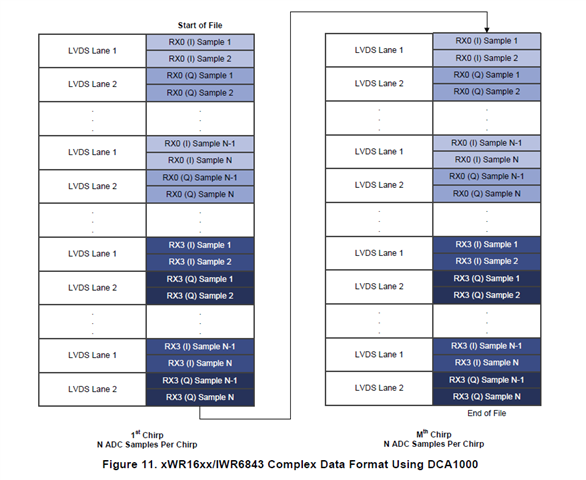

Input data rate is 600Mbps and two LVDS lanes are used

Please let us know the timing relations between DATA, CLK and FRCLK signals.