Does TMP121 support SPI Mode 3?

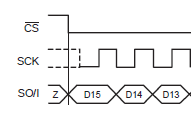

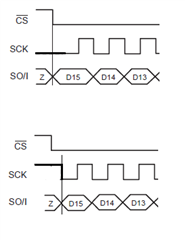

We see in the timing diagram that SCK is shown with a "dashed" falling edge indicating that the first SCK falling edge before the first SCK rising edge is ignored. However, this is not explicitly stated in the text.

The data sheet states: "Once CS is pulled low, temperature data from the last completed conversion prior to dropping CS is latched into the shift register and clocked out at SO on the falling SCK edge."