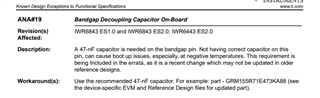

Other Parts Discussed in Thread: IWR6843,

Dears,

Customer have some question about power-on Sequence,

1. As shown in Figure 1 of the power-on sequence diagram in the chip datasheet, it takes 3ms for the chip to be powered on and reset. Does the power-on reset time refer to the time from VIOIN(3.3V) to NRESET VIH(3.3V Mode)1.57V(Figure 2)? As shown in the following figure

2. When the IC starts, whether there is any requirement on the power-on climbing time (0V to 3.3V stable) of VIOIN(3.3V stable)

3. The chip starts. Do the VIOIN (3.3V), VIOIN_18DIFF (1.8V), VDDIN (1.2V), VIN* (1.8V, LDO1V) multicircuit power supplies shown in Figure 1 have time sequence requirements?

4. If the chip is in flash startup mode, is there any requirement on the POWER failure time sequence (POWER DOWN 3ms marked on the right side of Figure 1)?

5. Some products sometimes start 350mS slowly (the comparison between the two products), what is the cause?

It is confirmed that there are differences in flash data: (the yellow channel at the top is abnormal products, while the green channel at the bottom is normal products)

the SCLK clock had intermittent phenomenon, and the difference was about 350ms, which was basically consistent.