Hello,

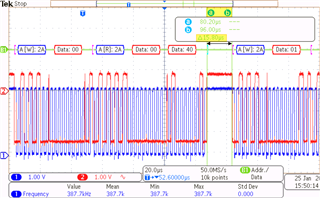

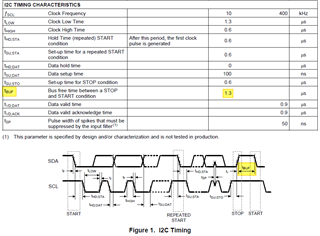

1) Looking at the I2C communication on the evaluation board LDC1614EVM shows a ~16us gap between the Register 0x00 (DATA0_MSB) and Register 0x01 (DATA0_LSB) readings. Is this a limitation of the LDC1614EVM since the LDC1614 specifies only 1.3us?

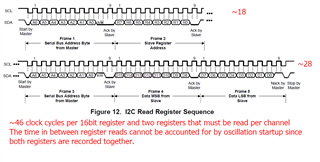

2) Does each register require the five frames of I2C readings shown in "Figure 12. I2C Read Register Sequence" or can the "repeated start" be used as in the way the 2nd byte of each register is read?

3) I'm trying to figure out the absolute fastest way to read a single channel or two channels and it appears to be ~231us theoretically (~255us in practice) per channel at 400kHz I2C clock and t_BUF=1us. Is that correct?

4) Am I miss-reading the LDC161x datasheet or does it use the terms "MSB" and "LSB" to refer both to the bytes within each 16bit register as well as to the two data registers within each channel? In other words, each register DATAx_MSB is made up of MSB + LSB and each register DATAx_LSB is also made up of MSB + LSB. Is that correct, and if so, could you please inform the authors that this confusing?

Thank you,

Andrey