We want to design a single board, so we need to move the IWRL6432 bypass capacitors to the same layer as the SoC.

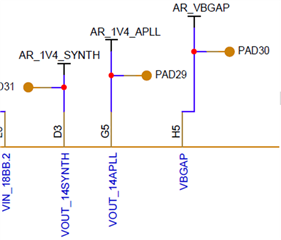

May I ask, are there any requirements for the bypass capacitors of the following 3 groups(14SYNTH、14APLL、VBGAP) of power supplies for the IWRL6432 in terms of layout placement, trace routing or impedance?