Other Parts Discussed in Thread: UNIFLASH,

Hi team,

Here's an issue from the customer may need your help:

1) A normal burn should switch to UART boot mode and requires 3 files UART_uniflash.release.tiimage, SBL_release.tiimage, appimage files. The first file, UART_uniflash.release.tiimage, is used to booting the two subsequent files to the fixed location in flash.

When in qspi boot mode, is it possible to only burn the .appimage file each time when update the firmware, leaving the SBL and UART_uniflash files unchanged? Or is it possible to switch boot mode through the registers without replacing the SOP?

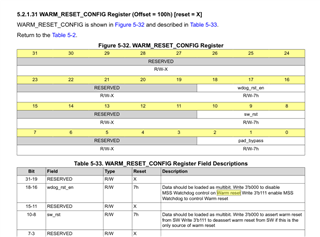

2) After the burn is complete, the AWR2944 needs to be reset to boot from flash again. How to implement a soft reset? And is there a reset method similar to the one mentioned in this doc?

3) The burn process through the serial interface is slow and takes about 1 minute. Serial mode is interrupt mode and readmode is block, so you need to pause DPC and frame first and then restart after the burn is complete. How to achieve that?

4) As mentioned in Q1, UART_uniflash.release.tiimage temporarily stores the .appimage file received from the serial port and writes it to flash by allocating a piece of memory in DSS L3. How to request memory on DSS through the MCU's program while the board is working? Is there any function that can see the current memory usage of the 2944?

Could you help look into this case? Thanks.

Best Regards,

Cherry