Hi team,

Here's an issue from the customer may need your help:

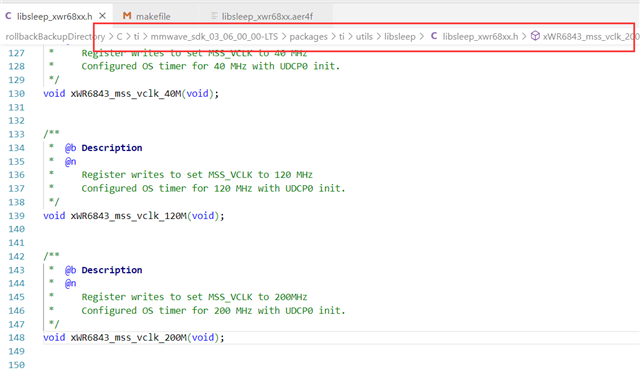

Requirement: After power up, change the division factor and clock source of the clock branch of MSS_VCLK after an event.

The configuration fields for the divider and clock source corresponding to the MSS_VCLK clock branch in the 520e document are as follows:

- CLKSRCSEL1.VCLKCLKSRCSEL is used to configure the clock source for MSS_VCLK

- CLKDIVCTL0.VCLKDIV is used to configure the division factor of MSS_VCLK (both fields are readable and writable)

And referenced to this thread, some of these fit the customer's application scenario, but they need more details on the configuration of these two register fields, for example:

Based on the above reply, if the chip power-up process has been completed, can this configuration step be set while the mss_subsystem is in a non-reset state? i.e. what is the chip state required for changes to the VCLKDIV and VCLKSRCSEL fields?

Could you help look into this case? Thanks.

Best Regards,

Cherry