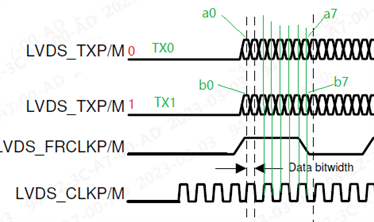

We are acquiring raw data of 2944 (in legacy LVDS mode): 1 lvds_clk , 1 lvds_frclk, 2 lvds_tx( i.e. lvds tx0 and lvds_tx1).

We are not sure how data bit is transferred on tx0 and tx1.

For example, data0 and data1 are sent out ( both data0 and data1 are 8-bit):

1)Which bits are sent on tx0, and which are on tx1? (MSB first)

As shown in the image attached, bit a0~a7 on tx0, bit b0~b7 on tx1, how these 16 bits are combined to 2 bytes?

2) Is the first bit sent at the rising edge of lvds_clk, or falling edge of lvds_clk?

3) Is the first bit sent out when lvds_frclk = 1?

Could you please give us a timing diagram about lvds_clk, lvs_frclk, and lvds_tx0&1?