Other Parts Discussed in Thread: AWR6843

Hi Team,

Here's an issue from the customer may need your help:

The question is based on the following two premises:

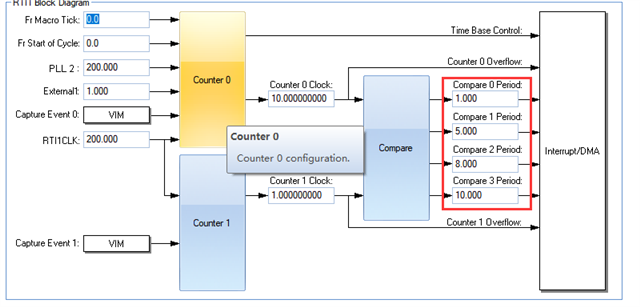

A. Free running counter 0/1 is an overflow interrupt generated when UC0/1 = RTICUC0/1 accumulates 1 and when the count reaches the 0xffff_ffff boundary.

B. Also, a compare int0/1/2/3 interrupt is generated when Free running counter 0/1 = RTICOM0/1.

Issues:

1) An overflow interrupt is an exception, so to avoid an overflow interrupt, is it required to clear Free running counter 0/1 when a compare interrupt occurs?

However, the customer did not find the correspond code in the SDK and the declaration RTIFRC1_FRC0/1_bit_end in the .h file was not referenced.

2) Given some differences in interrupt response times, how to make sure the timer outputs exactly as set if the under the above case?

3) If the Free running counter 0/1 is not cleared by a compare interrupt, the overflow interrupt is generated periodically, is it normal? And in this case, how to generate a compare int0/1/2/3 with different timestamp information? (since the count period for Free running counter 0/1 is fixed at this time)

Could you please help look into this case? Thanks.

Best Regards,

Cherry