Hi

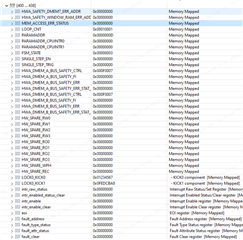

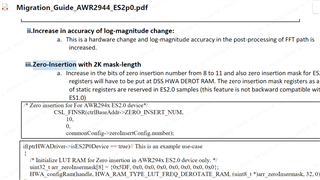

We tried ES2.0 in 2944, and found that there are some issues when trying to use zero-insertion function of HWA, in migration guide of ES2.0, we found that there are some updates about HWA, and we found two problems:

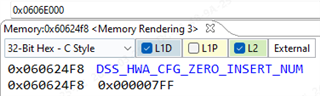

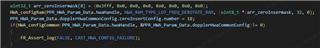

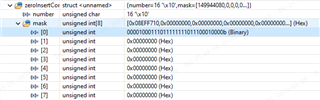

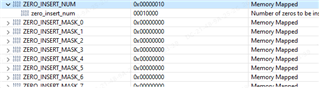

a. In this document, it says"Increase in the bits of zero insertion number from 8 to 11",but we found in SDK, the bit of number is still 8

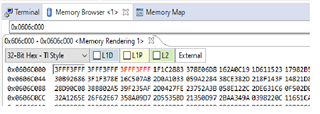

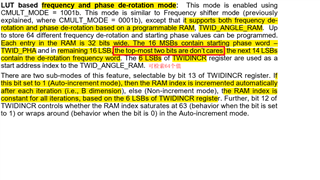

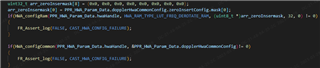

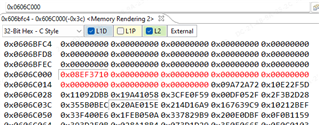

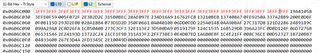

b.we can't config zero insertion mask registers as what we want, only the first 11 of the 16 bits can be configured.

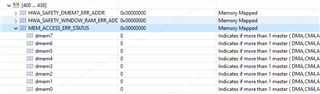

we try to config a 0xffff into DSS HWA DEROT RAM, but we only read 0x3fff in this RAM

Thanks