A. SPI Sample Rate Range

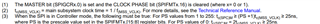

In the DATASHEET, you can know that the system clock is 40MHz no matter it is generated internally or an external oscillator is installed.

And SPICLK is adopted in two modes from the document:

1) Controller mode: SPICLK is generated inside the IC.

2) Peripheral mode: SPICLK is received by external clock source input.

[Q] What is the SPI sampling rate range of these two modes?

[A]*The following is the current understanding, please help to correct any mistakes.

1) Controller mode:

Range => ?? Hz[=1/256tc(VCLK)] ~ 40MHz[=1/25ns]

*What is the parameter [tc(VCLK)]?

2) Peripheral mode: determined by the external clock source input, the maximum is 40MHz[=1/25ns].

Range => 0 ~ 40MHz[=1/25ns]

B. Sampling rate Control method

[Q] How to control the sampling rate of the two modes of SPI?