Other Parts Discussed in Thread: SYSCONFIG,

Dear TI experts,

It brings us Config 1, 2, 3. with present LSDK5104,

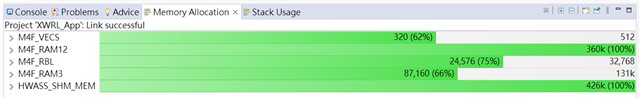

examples\mmw_demo\motion_and_presence_detection\xwrL64xx-evm\m4fss0-0_freertos\ti-arm-clang\linker.cmd:

seems it is like Config 3, but L3 as HWASS_SHM_MEM only 256KB

MEMORY

{

M4F_VECS : ORIGIN = 0x00400000 , LENGTH = 0x00000200

M4F_RAM : ORIGIN = 0x00400200 , LENGTH = 0x0007FE00

HWASS_SHM_MEM : ORIGIN = 0x60000000, LENGTH = 0x00040000

}

My question is, I want to use "Config 1", make M4F_RAM -> 768KB.

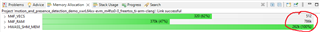

I try to set M4F_RAM : ORIGIN = 0x00400200 , LENGTH = 0x000BFE00

also extend both CONFIG_MPU_REGION1 & 2 : Region Size to 1MB in SYSCONFIG UI,

but it can not work...