Hi,

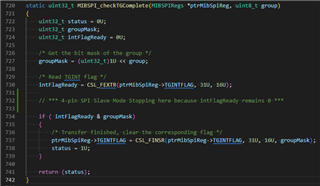

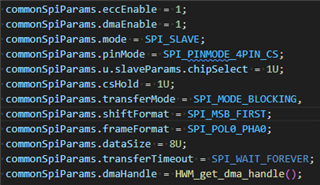

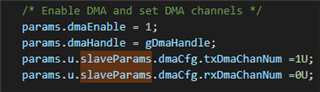

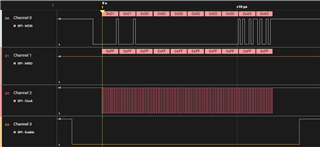

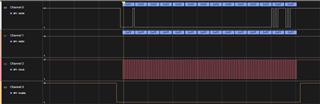

I am busy setting up SPI (slave mode) on a IWR1843BOOST board to prototype SPI communications we wish to do. I have read through the doxygen files as well as the test examples. To test my code, I have set up a STM32 Nucelo board as a SPI master. When using 3 pin mode (SPI_PINMODE_3PIN) my code operates correctly and I am able to read data from the master. However, when in 4 pin mode (SPI_PINMODE_4PIN_CS) the code either hangs, or times out depending if I include a transfer timeout or not. I presume the code is waiting for a HW signal that I know is being sent (confirmed with logic analyser - see picture below) and I am sure that I have the pinmux settings correct (see below). I am therefore at a loss as to why the 4-pin mode isn't working and am hoping someone on this forum can point me in the right direction? I will be happy to share more code as/if required.

A further question I have, is does the driver support multiple reads for a single write? That is, let's say I send 12 bytes of data with a single SPI master write operation and want to read the first two bytes, do something with them (very quickly) and then resume reading the remaining 10 bytes. I haven't managed to get this working either. I am able to read the first two bytes (in 3-pin mode), but when I try read the remaining 10 bytes using the SPI_transfer function, the code waits forever and only resumes when a new SPI write operation is initiated by the master.

Thank you in anticipation.

/* SPIA_MOSI */

Pinmux_Set_OverrideCtrl(SOC_XWR18XX_PIND13_PADAD, PINMUX_OUTEN_RETAIN_HW_CTRL, PINMUX_INPEN_RETAIN_HW_CTRL);

Pinmux_Set_FuncSel(SOC_XWR18XX_PIND13_PADAD, SOC_XWR18XX_PIND13_PADAD_SPIA_MOSI);

/* SPIA_MISO */

Pinmux_Set_OverrideCtrl(SOC_XWR18XX_PINE14_PADAE, PINMUX_OUTEN_RETAIN_HW_CTRL, PINMUX_INPEN_RETAIN_HW_CTRL);

Pinmux_Set_FuncSel(SOC_XWR18XX_PINE14_PADAE, SOC_XWR18XX_PINE14_PADAE_SPIA_MISO);

/* SPIA_CLK */

Pinmux_Set_OverrideCtrl(SOC_XWR18XX_PINE13_PADAF, PINMUX_OUTEN_RETAIN_HW_CTRL, PINMUX_INPEN_RETAIN_HW_CTRL);

Pinmux_Set_FuncSel(SOC_XWR18XX_PINE13_PADAF, SOC_XWR18XX_PINE13_PADAF_SPIA_CLK);

/* SPIA_CS */

Pinmux_Set_OverrideCtrl(SOC_XWR18XX_PINE15_PADAG, PINMUX_OUTEN_RETAIN_HW_CTRL, PINMUX_INPEN_RETAIN_HW_CTRL);

Pinmux_Set_FuncSel(SOC_XWR18XX_PINE15_PADAG, SOC_XWR18XX_PINE15_PADAG_SPIA_CSN);

/* SPI_HOST_INTR - not used, reference code */

Pinmux_Set_OverrideCtrl(SOC_XWR18XX_PINP13_PADAA, PINMUX_OUTEN_RETAIN_HW_CTRL, PINMUX_INPEN_RETAIN_HW_CTRL);

Pinmux_Set_FuncSel(SOC_XWR18XX_PINP13_PADAA, SOC_XWR18XX_PINP13_PADAA_SPI_HOST_INTR);