Hi,

What is the accuracy (jitter) of the frame period in IWR1443 Demo "mmwave_sdk_02_01_00_04/packages/ti/demo/xwr14xx/mmw/" of SDK 2.1.0.4?

Best regards,

Hiroyuki Taguchi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

What is the accuracy (jitter) of the frame period in IWR1443 Demo "mmwave_sdk_02_01_00_04/packages/ti/demo/xwr14xx/mmw/" of SDK 2.1.0.4?

Best regards,

Hiroyuki Taguchi

Hi Josh,

Thank you for your reply.

I would like to know how much fluctuations occur for the frame periodicity setting in the frameCfg command,

I didn't know where it was described in <MMWAVE_SDK2_INSTALL_DIR>/packages/ti/control/mmwavelink/docs/doxygen, so please let me know.

Best regards,

Hiroyuki

Hi Hiroyuki,

I apologize, you can find the frame periodicity info on this page: <MMWAVE_SDK2_INSTALL_DIR>/packages/ti/control/mmwavelink/docs/doxygen/html/structrl_frame_cfg__t.html

Best Regards,

Josh

Hi Josh,

Thank you for your reply.

I understand that the frame period setting is 1LSB=5ns.

Since it can be set with an accuracy of 5ns, it can be assumed that the frame period accuracy of actual operation is also 5ns.Is this understanding correct?

And please tell me more.

5ns corresponds to one cycle of the 200MHz clock.

I think that the circuit counts the timer with the 200MHz clock and starts the frame with the Timer tick as the trigger.

If the IWR1443 tries to achieve a frame period accuracy of 5 ns, I think that it will be impossible to achieve it if software processing is performed from the Timer tick.

I presume that the pulse generated by the timer tick is directly input to the frame start processing circuit by hardware without going through software processing.

Is this guess correct?

Best regards,

Hiroyuki

Hi Hiroyuki,

I believe this is correct but please allow me to confirm internally and get back to you with more info tomorrow.

Best Regards,

Josh

Hi Hiroyuki,

Very sorry about the delay here. I'm still waiting on an answer from my systems team. Please expect a response early next week. Thank you again for your patience.

Best Regards,

Josh

Hi Josh,

What is the situation of this question?

Please update me [us] on the current situation.

Hiroyuki

Hi Hiroyuki,

I apologize, I'm having a hard time getting the answers out of the relevant folks. I am still working to get you confirmation here. Your patience is appreciated.

Thank you,

Josh

Hi Hiroyuki,

Sorry again for the delay. I have managed to get some more information regarding this.

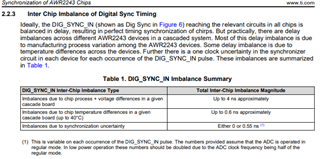

If software triggered frame is used, it is very difficult to predict the uncertainty. If hardware trigger is used for triggering the frame through Dig_Sync_in pin then you could refer below.

You could refer below appnotes.

https://www.ti.com/lit/an/swra574b/swra574b.pdf

For single chip timing uncertainty is less than 0.55ns, for cascading it could be up to 4ns.

Best Regards,

Josh