Hi,

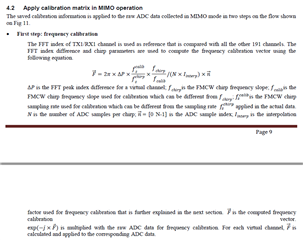

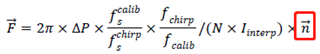

In signal_processing_4chip_cascade.pdf, the following frequency calibration process is introduced.

The vector n indicates that the frequency deviation increases linearly from the first ADC sampling point to the last ADC sampling point.

1. What are the sources of frequency deviation? From the calibration formula, it looks like the deviation of the FM slope. Is this the case? If yes, why the slopes of different channels under the same device are different? If not, why does the frequency error increase linearly with the ADC sampling order?

2. Will there be time asynchrony between channels? If yes, will it have an impact?

The absolute value of delta P increases linearly. For example, if there are 256 ADC sampling points, the offset of the 256th point is 256 times that of the first point. This seems to be caused by the different FMCW slopes of Tx and Rx. Is this the source of the deviation?