Hello,

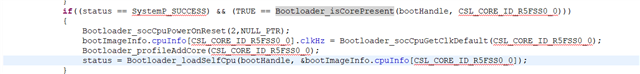

I'm getting data abort exception during the initialization of Autosar OS after QSPI SBL

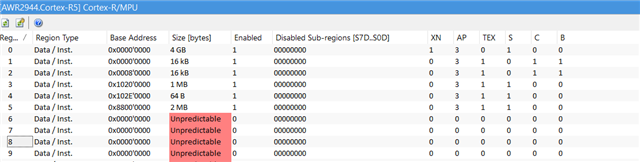

According to data fault registers, it should be synchronus external abort due to write access but I'm not able to pinpoint the root cause because it happens in different places Everytime and debugging/stepping through the code delay the issue.

Also data fault address register points to strange address 0xfffffff8 which contains nothing.

Any idea what could be the reason or how to debug further?

Update:

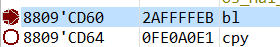

After further investigation it seems that BL instruction with machine code "2AFFFFEB" and offset "8809CD60"causing the issue.

When I checked the instruction,code and offset, it's basically gonna jump to valid address which is located in map file and refer to specific symbol.

Is there compiler support here who can take a look at this?