Hello All

I hope you are fine

I would to ask a few questions regarding the CRC HW engine section 21.6 in AWR294x Technical Reference Manual v1.0

I am intending to use the FULL-CPU mode, thus I would to understand the following:

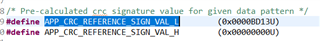

1- In order to verify the CRC signature, the CPU can read from the PSA Signature Register and compare the calculated signature to the pre-determined CRC signature value

Question is: What is meant by the "pre-determined CRC signature value" and how is it calculated ?

Because in my design, the data stored in the memory are NOT deterministic data but rather changeable based on the radar measurements. So how can I get a pre-determined CRC value for them ?

2- When to use MSS_CRC base address and when to use DSS_CRC base address ?

As I see that the registers defined in "21.6.6 MSS_MCRC Registers" are only for MSS_CRC not DSS_CRC.

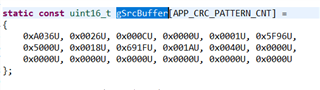

3- In TI CRC example located in mcu_plus_sdk_awr294x_08_06_00_28\examples\drivers\crc\crc_16bit

what is meant by gSrcBuffer ? is it just a data input example and that's it ?

4- How did you calculated the value for APP_CRC_REFERENCE_SIGN_VAL_L and APP_CRC_REFERENCE_SIGN_VAL_H ?

I think that's it for now.

Please advise and many thanks in advance