Other Parts Discussed in Thread: DCA1000EVM, AWR2944

Our customer wants to use AWR2944EVM and DCA1000EVM to get ADC data with 4TX and 4RX. In particular, they want to make a MIMO measurement that switches every single Tx.

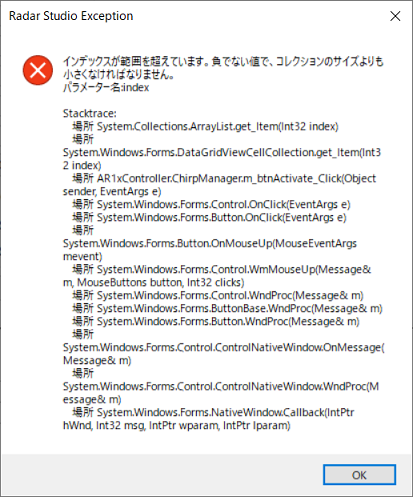

They were able to get the data using the mmWave Studio 3.1.1, but the Chirp Manager cannot be activated with an error, so they don't know if the Tx is switched.

The settings in the mmWave Studio 3.1.1 are summarized below. The default values are used for all settings except as noted.

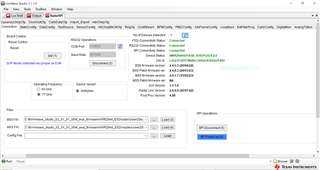

1. The firmware is located at the following location (C:\ti\mmwave_studio_03_01_01_00\rf_eval_firmware\AWR2944_ES2)

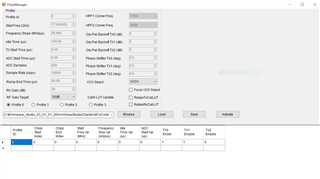

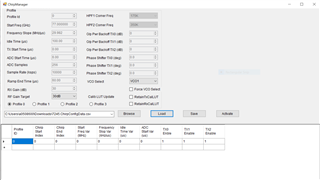

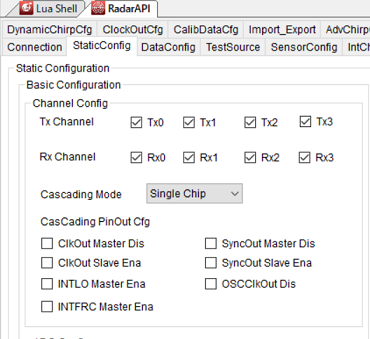

2. In the StaticConfig tab, under "Static Configuration"-"Basic Configuration"-"Channel Config", add checks for Tx2 and Tx3.

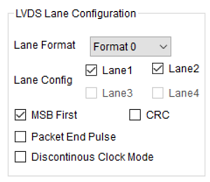

3. In the DataConfig tab, under "LVDS Lane Configuration"-"Lane Config", add a check for Lane 2.

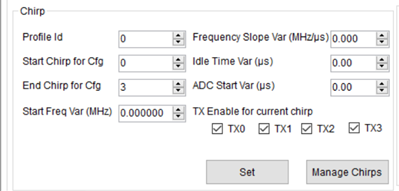

4. In the SensorConfig tab, under "Sensor Configuration"-"Chirp"-"TX Enable for current chirp", add checks for TX2 and TX3 and set "End Chirp for Cfg" to 3.

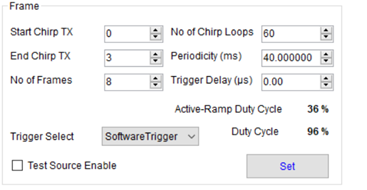

5. In the SensorConfig tab, under "Sensor Configuration"-"Frame", set "End Chirp TX" to 3 and "No of Chirp Loops" to 60.

Could you tell me the necessary settings?

Best regards,

Daisuke