Hi Team,

Is there any way to verify that the test source is enabled as we encountered that the ADC data captured is not correct.

Thanks

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Andy -

Thanks for the post and welcome to E2E!

Perhaps you can read this register after setting it (and after also of course, writing the config register, too)

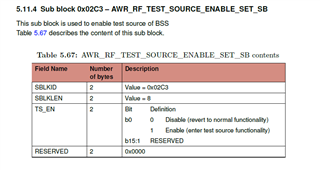

This is from the ICD manual, located in the docs folder of the SDK, and on the product page

https://www.ti.com/tool/download/MMWAVE-DFP-2G , please scroll down slightly to see documentation links.

Hi Josh,

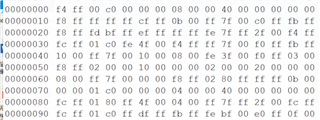

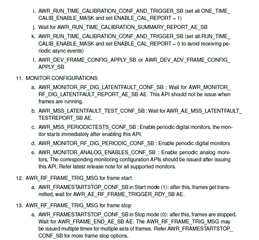

Thanks for your reply. We have tried again and read such register which is shown as below:

I think the register is correct, but it doesn't give any response.

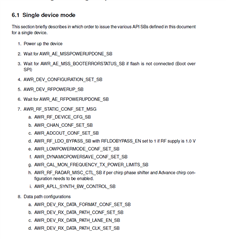

The configuration of the test source is shown below:

However, the captured ADC data is combined of CP value and raw ADC data in the format of RAW14. The CP value seems correct but the ADC raw data seems not correct. Most of the captured data are the minimum or the maximum.

As the test source is set open, the ADC data should not be affected by the RF module. is there any possible problem that makes the data wrong?

In addition, is it reliable for the thought that as the Cp data is correct, the transmission of the data (the configuration of the CSI2 datapath) is without error?

Andy

Hello,

How are you capturing the data, is it with the AWR2243BOOST and DCA1000 or is it with a custom board? If there is an issue, it is either with the test source configuration or the CSI2 data capture, the test source does not use the RF front end.

Regards,

Adrian

Hi Adrian,

Thanks for your reply!

We used our custom board and tried to capture ADC data and the chirp parameter data using CSI2. We found the chirp parameter data is correct with wrong ADC data with test source on.

Therefore, our questions are:

1. Is there any suggested monitors or some commands can be used for diagnosing the problem?

2. Could we get to the conclusion that the CSI2 data lane is w/o problems if we get the correct chirp parameter sent out?

3. Could you please help to verify the configuration of the test source as set in the last thread or is there any possible methods to verify that the configuration of the test source is correct?

Many Thanks

Andy

Hello Andy,

Can you please provide your sequence of mmwavelink API commands from start to end, similar to something like below?

We should first verify that you are following the correct API sequence. Once this is verified, then we will need to look further into how you are capturing and parsing the data.

Another thing you should check is that you are not exceeding the throughput of the CSI2 interface. You can calculate this like below:

Data rate required = (numADCSamples*numBitsPerSample*numRX)/(idleTime+RampEndTime)

Assuming 1024 samples, 16 bits per sample, 4 RX, 2uS idle time, 32.9us ramp end time

(1024*16*4)/(34.9*10^-6) = ~ 1878 Mbps

Max throughput = NumCSI2Lanes * CSI2DataRate

Assuming 600Mbps with four lanes, 600*4 = 2400 Mbps

Regards,

Adrian

HI Adrian,

Thanks for your reply!

We take 256 samples per chirp in the format of complex1x with 14 bits per sample. The clock is set to 600MHz with four CSI2 lanes on.

Therefore, the number of bits per sample is

256 * 4 * 2 *14 = 28672 bits;

The ramp end time is 60us and the idle time is set to 10us, therefore, the chirp time is 70us;

The actual output rate is

28672 / 70 = 409.6 Mbps

which is slower than the set rate;

for the sequence it is shown below:

1. Power up the device

2. Wait for AWR_AE_DEV_MSSPOWERUPDONE_SB

3. Wait for AWR_AE_MSS_BOOTERRORSTATUS_SB

4. AWR_DEV_CONFIGURATION_SET_SB

5. AWR_DEV_RFPOWERUP_SB

6. Wait for AWR_AE_RFPOWERUPDONE_SB

7. AWR_RF_STATIC_CONF_SET_MSG

8. AWR_RF_DEVICE_CFG_SB

9. AWR_CHAN_CONF_SET_SB

10. AWR_ADCOUT_CONF_SET_SB

11. AWR_RF_LDO_BYPASS_SB with RFLDOBYPASS_EN set to 1 if RF supply is 1.0 V

12. AWR_LOWPOWERMODE_CONF_SET_SB

13. AWR_RF_RADAR_MISC_CTL_SB if per chirp phase shifter and Advance chirp configuration needs to be enabled.

14. AWR_APLL_SYNTH_BW_CONTROL_SB

15. AWR_DEV_RX_DATA_FORMAT_CONF_SET_SB

16. AWR_DEV_RX_DATA_PATH_CONF_SET_SB

17. AWR_DEV_RX_DATA_PATH_CLK_SET_SB

18. AWR_HIGHSPEEDINTFCLK_CONF_SET_SB

19. AWR_DEV_CSI2_CFG_SET_SB

20. AWR_RF_INIT_MSG

21. Wait for AWR_AE_RF_INITCALIBSTATUS_SB

22. AWR_RFINIT_SB:

23. AWR_PROG_FILT_COEFF_RAM_SET_SB

24. AWR_PROG_FILT_CONF_SET_SB

25. AWR_CHIRP_CONF_SET_SB

26. AWR_FRAME_CONF_SET_SB

27. AWR_DEV_FRAME_CONFIG_APPLY_SB

28. AWR_RF_FRAME_TRIG_MSG

29. AWR_FRAMESTARTSTOP_CONF_SB

30. wait AWR_AE_RF_FRAME_TRIGGER_RDY_SB

Thanks

Andy

Hello,

Thanks, overall your sequence looks correct except I do not see the AWR_RF_TEST_SOURCE_CONFIG_SET_SB and AWR_RF_TEST_SOURCE_ENABLE_SET_SB being called. Are you calling these APIs and at which point are you calling them?

Regards,

Adrian