Hi Team,

Follow the manual to configure AWR2243 via SPI and receive a response from Frame Trigger Ready and Frame end of RF_Async_event_MSG1 when FrameStart is enabled. But there are no signal outputs from CLK and line on CSI interface.

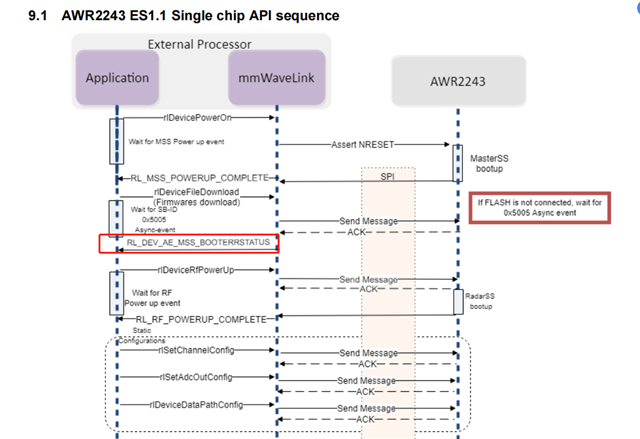

The flow is as follows:

1) Controls AWR2243 reset pin, waits for MSS_powerup_complete reply with a missing MetaHerer status.

2) The firmware array in the xwr22xx_metaImage.h file is loaded via SPI, and each packet is sent with an ACK reply, and there is no MSS_BOOTERRSTATUS reply as shown in the red box on the left of the figure below. The red box on the right side of the figure below tells you to wait for a 0x5005 event if no Flash is connected. Customer is currently designing to connect a flash via QSPI, will there be no response from MSS_BOOTERRSTATUS? How to determine if the firmware was loaded successfully after loading the firmware?

3) Enable RF PowerUp to receive the data replies: ba dc cd ab 36 a0 22 00 0c 00 00 00 01 00 9a 5f 01 50 14 00 fb fe 3b 07 76 50 21 00 10 00 00 00 00 00 00 00 20 61

4) Configure Static_Conf_Set related register:

a. AWR_RF_DEVICE_CFG_SB configure ASYNC_EVENT_DIR为BSS TO HOST

Configure MONITORING_ASYNC_EVENT_DIR to BSS TO HOST

Enable FRAME_START_ASYNC_EVENT and FRAME_STOP_ASYNC_EVENT

Enable INTER_BURST_POWER_SAVE

Turn off WDT

Set ASYNC_EVENT_CRC to 32bit

b. AWR_CHAN_CONF_SET_SB Enable 4-way RX and TX0

Configure to single Chip mode

Turn off FM_CW_CLKOUT_MASTER, FM_CW_SYNCOUT_MASTER, FM_CW_CLKOUT_SLAVE, FM_CW_SYNCOUT_SLAVE, INTLO_MASTER, INTFRC_MASTER

Open OSCCLKOUT(which is used to source the external FPGA clock )

c. AWR_ADCOUT_CONF_SET_SB configure adc to 12bit, Reduse Full Scale Bits is 0 and only real

d. AWR_RF_RADAR_MISC_CTL_SB all configured to 0

5) DATA_PATH setting:

a. AWR_DEV_RX_DATA_FORMAT_CONF_SB The data format for ADC is configured as needed

b. AWR_DEV_RX_DATA_PATH_CONF_SET_SB is configure to CSI interface mode

c. AWR_DEV_RX_DATA_PATH_CLK_SET_SB is configured to CLK_DDR mode and the rate is 150M

d. AWR_HIGHSPEEDINTFCLK_CONF_SET_SB is configured to 300M

e. AWR_DEV_CSI2_CFG_SET_SB: Per default Lane0 at Pos1, Lane1 at Pos2, Lane2 at Pos4, Lane3 at Pos5, CLK at Pos3, all wires are set to POL_plus; LineStartEnd is enabled

6) Configure RF init, the data waiting to reply to RF_AE_INITCALIBSTATUS_SB is ba dc cd ab 32 20 28 00 0c 04 00 00 01 00 98 db 04 10 18 00 fe 0f 00 80 fc 0f 00 00 23 00 00 00 3b 04 00 00 0f 00 00 00 c7 aa 9e 4d.

7) Configure Profile information and the sampling point is 64.

8) Configure CHIRP_CONF_set, bind Profile0, ChirpStartIndex and ChirpEndIndex are 0, set only 1 chirp

9) Configure AWR_frame_CONF_SB, ChirpStartIndex and ChirpEndIndex are 0, NumLoops is 1 and NumFrames is 64

10) Configure AWR_DEV_FRAME_CONF_SB, NumChirps is 64 and HalfWordsPerChirp is 64(sampling point is 64 and transfer real only)

11) Enable FrameStart to receive Frame Trigger Ready for RF_Async_event_MSG1 and wait a while for a reply to the Frame end again

Could you help check this case? Thanks.

Best Regards,

Cherry