Hi expert,

Customer report a issue. The memory content will be altered randomly. They provide a simple test code for reproducing issue.

1. import SBL demo project from SDK5.3.

2. switch to release build. (debug build has issue as e2e: https://e2e.ti.com/support/sensors-group/sensors/f/sensors-forum/1268005/iwrl6432boost-sbl-issue-in-sdk5-3

3. replace the content of sbl_main.c as attached fie, recompile code, program device and run it. (or run code in CCS)

/*

* Copyright (C) 2023 Texas Instruments Incorporated

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

#include "kernel/dpl/DebugP.h"

#include "kernel/dpl/AddrTranslateP.h"

#include "board/flash.h"

#include "drivers/hw_include/cslr_soc.h"

#include "drivers/hw_include/hw_types.h"

#include "ti_drivers_open_close.h"

#include "ti_board_open_close.h"

#include "ti_board_config.h"

#include "sbl.h"

#include "app_errors.h"

#include "bootload.h"

#include "parser.h"

/**************************************************************************

*************************** Global Variables *****************************

**************************************************************************/

sbl_Obj_t sblObj;

/**************************************************************************

*************************** Local Definitions ****************************

**************************************************************************/

volatile uint32_t appBootVec __attribute__ ((section (".jumptoAppdata")));

volatile uint32_t* vtor __attribute__((section (".jumptoAppdata")));

volatile uint32_t* appShmClk __attribute__ ((section (".jumptoAppdata")));

volatile uint32_t* topPrcmShmCfg __attribute__ ((section (".jumptoAppdata")));

void sbl_switchtoapp()

{

vtor = (volatile uint32_t*)0xE000ED08;

appShmClk = (volatile uint32_t*)0x56060398;

topPrcmShmCfg = (volatile uint32_t*)0x5A040500;

appBootVec = t_Metaheader.w_BootVector;

*vtor = t_Metaheader.w_BootVector;

if(t_Metaheader.w_ShMemAlloc == 0)

{

// Disable APP CLK and HWA CLK for shared RAM

*appShmClk = 0x0;

// Configure the Shared RAM

*topPrcmShmCfg = ((*topPrcmShmCfg & ~CSL_TOP_PRCM_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_APPSS_CONFIG_MASK) | 0x0);

*appShmClk = 0x5;

}

else if (t_Metaheader.w_ShMemAlloc == 1)

{

// Disable APP CLK and HWA CLK for shared RAM

*appShmClk = 0x0;

// Configure the Shared RAM

*topPrcmShmCfg = ((*topPrcmShmCfg & ~CSL_TOP_PRCM_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_APPSS_CONFIG_MASK) | 0x7);

*appShmClk = 0x6;

}

else if (t_Metaheader.w_ShMemAlloc == 2)

{

// Disable APP CLK and HWA CLK for shared RAM

*appShmClk = 0x0;

// Configure the Shared RAM

*topPrcmShmCfg = ((*topPrcmShmCfg & ~CSL_TOP_PRCM_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_APPSS_CONFIG_MASK) | 0x38);

*appShmClk = 0x9;

}

else if (t_Metaheader.w_ShMemAlloc == 3)

{

// Disable APP CLK and HWA CLK for shared RAM

*appShmClk = 0x0;

// Configure the Shared RAM

*topPrcmShmCfg = ((*topPrcmShmCfg & ~CSL_TOP_PRCM_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_REG_HWA_PD_MEM_SHARE_APPSS_CONFIG_MASK) | 0x3f);

*appShmClk = 0xA;

}

else

{

}

__asm(" MSR MSP, %0" : :"r" ((uint32_t)*(uint32_t*)appBootVec));

__asm("BX %0"::"r" ((uint32_t)*(uint32_t*)(appBootVec + 4)));

}

void sbl_computeCrc32Cpu(uint32_t* data, uint32_t numbytes, uint32_t* crc32)

{

uint32_t loopCnt, patternCnt, baseAddr;

CRC_Channel_t chNumber;

CRC_SignatureRegAddr psaSignRegAddr;

uint32_t app_crc_sect_cnt = 1U;

uint32_t app_crc_watchdog_preload_val = 0U;

uint32_t app_crc_block_preload_val = 0U;

uint32_t app_crc_type = CRC_TYPE_32bit;

uint32_t app_crc_data_size = CRC_DW_32bit;

uint32_t app_crc_bit_swap = 1;

uint32_t app_crc_byte_swap = 0;

CRC_Signature calcrc;

/* Configure CRC parameters */

baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

patternCnt = (numbytes / 4);

chNumber = CRC_CHANNEL_1;

/* Get CRC PSA signature register address */

CRC_getPSASigRegAddr(baseAddr, chNumber, &psaSignRegAddr);

/* Initialize and Configure CRC channel */

CRC_initialize(baseAddr, chNumber, app_crc_watchdog_preload_val, app_crc_block_preload_val);

CRC_configure(baseAddr, chNumber, patternCnt, app_crc_sect_cnt, CRC_OPERATION_MODE_FULLCPU, app_crc_type, app_crc_data_size ,app_crc_bit_swap, app_crc_byte_swap);

/* Reset the CRC channel*/

CRC_channelReset(baseAddr, chNumber);

/* compute the CRC by writing the data buffer on which CRC computation is needed */

for (loopCnt = 0; loopCnt < patternCnt ; loopCnt++)

{

HW_WR_REG32(psaSignRegAddr.regL, data[loopCnt]);

}

/* Fetch CRC signature value */

CRC_getPSASig(baseAddr, chNumber, &calcrc);

*crc32 = calcrc.regL;

return;

}

void sbl_configureCrc32Cpu()

{

uint32_t baseAddr,patternCnt;

CRC_Channel_t chNumber;

uint32_t app_crc_sect_cnt = 1U;

uint32_t app_crc_watchdog_preload_val = 0U;

uint32_t app_crc_block_preload_val = 0U;

uint32_t app_crc_type = CRC_TYPE_32bit;

uint32_t app_crc_data_size = CRC_DW_32bit;

uint32_t app_crc_bit_swap = 1;

uint32_t app_crc_byte_swap = 0;

/* Configure CRC parameters */

baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

chNumber = CRC_CHANNEL_1;

patternCnt = 0;

/* Initialize and Configure CRC channel */

CRC_initialize(baseAddr, chNumber, app_crc_watchdog_preload_val, app_crc_block_preload_val);

CRC_configure(baseAddr, chNumber, patternCnt, app_crc_sect_cnt, CRC_OPERATION_MODE_FULLCPU, app_crc_type, app_crc_data_size ,app_crc_bit_swap, app_crc_byte_swap);

/* Reset the CRC channel*/

CRC_channelReset(baseAddr, chNumber);

}

void sbl_sendDataCrc32Cpu(uint32_t* data, uint32_t numbytes)

{

uint32_t loopCnt, patternCnt, baseAddr;

CRC_Channel_t chNumber;

CRC_SignatureRegAddr psaSignRegAddr;

/* Configure CRC parameters */

baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

patternCnt = (numbytes / 4);

chNumber = CRC_CHANNEL_1;

HW_WR_FIELD32(baseAddr + CRC_PCOUNT_REG1,

CRC_PCOUNT_REG1_PAT_COUNT1,

patternCnt);

/* Get CRC PSA signature register address */

CRC_getPSASigRegAddr(baseAddr, chNumber, &psaSignRegAddr);

/* compute the CRC by writing the data buffer on which CRC computation is needed */

for (loopCnt = 0; loopCnt < patternCnt ; loopCnt++)

{

HW_WR_REG32(psaSignRegAddr.regL, data[loopCnt]);

}

return;

}

uint32_t sbl_getCrc32Cpu()

{

uint32_t baseAddr;

CRC_Channel_t chNumber;

CRC_Signature calcrc;

/* Configure CRC parameters */

baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

chNumber = CRC_CHANNEL_1;

/* Fetch CRC signature value */

CRC_getPSASig(baseAddr, chNumber, &calcrc);

return calcrc.regL;

}

void sbl_computeCrc16Cpu(uint16_t* data, uint32_t numbytes, uint16_t* crc16)

{

uint32_t loopCnt, patternCnt, baseAddr;

CRC_Channel_t chNumber;

CRC_SignatureRegAddr psaSignRegAddr;

uint32_t app_crc_sect_cnt = 1U;

uint32_t app_crc_watchdog_preload_val = 0U;

uint32_t app_crc_block_preload_val = 0U;

uint32_t app_crc_type = CRC_TYPE_16bit;

uint32_t app_crc_data_size = CRC_DW_16bit;

uint32_t app_crc_bit_swap = 1;

uint32_t app_crc_byte_swap = 0;

CRC_Signature calcrc;

/* Configure CRC parameters */

baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

patternCnt = (numbytes / 2);

chNumber = CRC_CHANNEL_2;

/* Get CRC PSA signature register address */

CRC_getPSASigRegAddr(baseAddr, chNumber, &psaSignRegAddr);

/* Initialize and Configure CRC channel */

CRC_initialize(baseAddr, chNumber, app_crc_watchdog_preload_val, app_crc_block_preload_val);

CRC_configure(baseAddr, chNumber, patternCnt, app_crc_sect_cnt, CRC_OPERATION_MODE_FULLCPU, app_crc_type, app_crc_data_size ,app_crc_bit_swap, app_crc_byte_swap);

/* Reset the CRC channel*/

CRC_channelReset(baseAddr, chNumber);

/* compute the CRC by writing the data buffer on which CRC computation is needed */

for (loopCnt = 0; loopCnt < patternCnt ; loopCnt++)

{

HW_WR_REG16(psaSignRegAddr.regL, data[loopCnt]);

}

/* Fetch CRC signature value */

CRC_getPSASig(baseAddr, chNumber, &calcrc);

*crc16 = calcrc.regL;

return;

}

/*!

* @b Description

* @n

* This function download the application meta imageover over a device peripheral.

* It does the following:

* 1. Erases the portion of SFLASH where the Metaimage has to be stored.

* 2. Receives the Metaimage over transport interface.

* 3. Stores the image into the SFLASH.

*

* @param[in] qspiFlashHandle

* Handle of QSPI Flash module.

* @param[in] flashAddr

* Address of SFLASH location where the application meta image is written to.

*

* \ingroup SBL_INTERNAL_FUNCTION

*

* @retval

* Success - 0

* @retval

* Error - SBL Error code

*/

int32_t SBL_imageFlasher(Flash_Handle qspiFlashHandle, uint32_t flashAddr)

{

int32_t totDataLen = 0;

int32_t retVal = 0;

uint32_t numBlocksErase = 0;

uint32_t index, offset;

Flash_Attrs* attr;

SBL_printf("Debug: Erasing SFlash...\r\n");

attr = Flash_getAttrs(CONFIG_FLASH0);

/* Calculate the number of blocks to erase.*/

numBlocksErase = SBL_MAX_METAIMAGE_SIZE / (attr->blockSize);

offset = (flashAddr / (attr->blockSize));

/* Erase FLASH memory*/

for (index = 0; index < numBlocksErase; index++)

{

retVal = Flash_eraseBlk(qspiFlashHandle, (index + offset));

if(retVal != 0)

{

goto exitImageFlasher;

}

}

SBL_printf("Debug: Flash Erase complete\r\n");

totDataLen = SBL_transportDownloadFile (qspiFlashHandle, flashAddr, SBL_MAX_METAIMAGE_SIZE);

if (totDataLen < 0)

{

SBL_printf("Error: File download failed.\r\n");

retVal = totDataLen;

}

else

{

SBL_printf("Debug: Total data written = 0x%x\r\n", totDataLen);

}

exitImageFlasher:

return retVal;

}

/**************************************************************************

*************************** Function Definitions *************************

**************************************************************************/

#define HEAD_SYMBOL_NUMBER (3)

#define HEAD_BUFFER_SYSTEM (0)

#define FLASH_RWBUFFER_SIZE (24)

#define HEAD_SYMBOL_SYSTEM 'TDYS'

uint8_t gFlashModifyBuffer[HEAD_SYMBOL_NUMBER][FLASH_RWBUFFER_SIZE];

typedef struct CLI_confighead_t

{

/**

* @brief Configuration which was used to configure the CLI module

*/

uint32_t head_symbol;

/**

* @brief This is the number of CLI commands which have been added to the module

*/

uint32_t section_numbers;

/**

* @brief This is the number of CLI commands which have been added to the module

*/

uint32_t section_size_byte;

}CLI_confighead;

uint32_t command_buff[4];

void sbl_main(void *args)

{

/* Open drivers for peripherals*/

Drivers_open();

Board_driversOpen();

int32_t retVal = MINUS_ONE, downldSuccess = MINUS_ONE;

uint8_t autoboot = SBL_AUTOBOOT_COUNT;

uint8_t userInput = 0;

uint32_t efuseRow16 = 0;

DebugP_log("[MCSPI] Loopback example started ...\r\n");

uint32_t read_position = 0U;

uint32_t size = 0U;

uint32_t cnt = 0U;

// uint16_t CRC_cal;

CLI_confighead confighead;

size = sizeof(confighead);

read_position = read_position + size;

size = sizeof(uint32_t) * 4;

command_buff[0] = size - sizeof(uint32_t) ; //section size

command_buff[1] = 0;

command_buff[2] = 0;

command_buff[3] = 0xb;

memcpy(gFlashModifyBuffer[HEAD_BUFFER_SYSTEM] + read_position, command_buff, size);

read_position = read_position + size;

cnt++;

confighead.head_symbol = (uint32_t)HEAD_SYMBOL_SYSTEM;

confighead.section_numbers = cnt;

confighead.section_size_byte = read_position;

memcpy((uint8_t*)gFlashModifyBuffer[HEAD_BUFFER_SYSTEM], (uint8_t*)&confighead, sizeof(confighead));

DebugP_log("\r\nHEAD_SYMBOL_SYSTEM: %x\r\n", HEAD_SYMBOL_SYSTEM);

DebugP_log("HEAD_SYMBOL_SYSTEM (BUFFER) (After memcpy):");

uint32_t i;

for (i = 0; i < 28; i++)

{

DebugP_log("%x ", gFlashModifyBuffer[HEAD_BUFFER_SYSTEM][i]);

}

DebugP_log("\r\n");

while(1);

// SBL_printf ("\r\n");

// SBL_printf ("**********************************************\r\n");

// SBL_printf ("Secondary Bootloader Application Start \r\n");

// SBL_printf ("**********************************************\r\n");

// SBL_printf ("Press CR key or Space key to stop auto boot and Update Meta Image...\r\n");

// SBL_printf ("Loading existing Meta Image from Flash in ");

// efuseRow16 = HW_RD_REG32(CSL_TOP_EFUSE_U_BASE + CSL_TOP_EFUSE_EFUSE0_ROW_16);

// /* Read FEC Eclipse mode */

// if(((efuseRow16 >> 5) & 0x1U) == 0x1U)

// {

// sblObj.fecShRamPresent = 1;

// if (((efuseRow16 >> 6) & 0x1U) == 0x1U)

// {

// sblObj.fecEclipseMode = 1U;

// }

// else

// {

// sblObj.fecEclipseMode = 0U;

// }

// }

// do

// {

// retVal = SBL_transportRead((uint8_t*)&userInput, 1U);

// /* Stop autoboot only if the input character is CR key or Space key */

// if (retVal == 0)

// {

// if ((userInput != SBL_CR_KEY) && (userInput != SBL_SPACE_KEY))

// {

// retVal = MINUS_ONE;

// }

// }

// /* Check if user interrupted the autoboot */

// if (retVal == 0)

// {

// sblObj.metaimageUpdate = 1;

// SBL_printf ("\r\n\nUpdate Meta Image selected\r\n");

// }

// else

// {

// SBL_printf (" %d", autoboot--);

// continue;

// }

// }while((retVal != 0) && (autoboot != 0));

// if(sblObj.metaimageUpdate == 1)

// {

// SBL_printf ("\r\n Loading Application over UART...\r\n");

// downldSuccess = SBL_imageFlasher(gFlashHandle[CONFIG_FLASH0], M_META_IMAGE);

// if(downldSuccess == 0)

// SBL_printf ("\r\n Image Loading Successful...\r\n");

// else

// SBL_printf ("\r\n Image Loading Failed...\r\n");

// sblObj.metaimageUpdate = 0;

// }

// SBL_printf ("\r\n Booting the Application.\r\n");

// retVal = bootload_qspi(M_META_IMAGE);

// if(retVal != 0)

// {

// SBL_printf ("\r\n No Valid application found. Booting backup factory default image...\r\n");

// /* Perform Boot Loading of default image */

// retVal = bootload_qspi(M_META_IMAGE_BACKUP);

// }

// if (retVal == 0)

// {

// Board_driversClose();

// Drivers_close();

// sbl_switchtoapp();

// }

// else

// {

// SBL_printf ("\r\n No Valid Image found in flash. Try loading Valid Application...\r\n");

// }

}

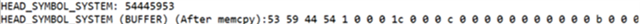

The expect result will be

However, the output from the test code is wrong.

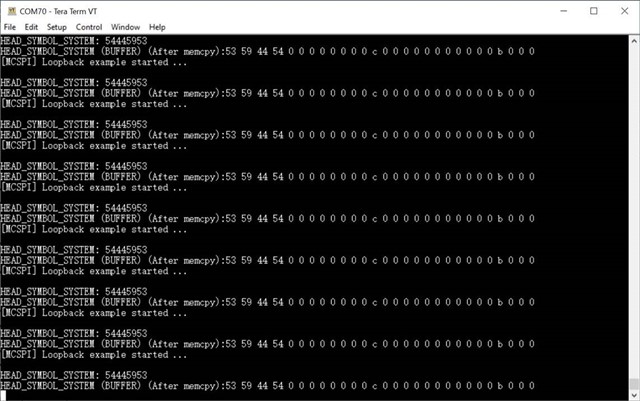

I also can reproduce this issue on EVM. After some deep dive, I found the memory content will be change during print out information.

This is memory dump from CCS just after 2nd memcoy call (line 384)

However, in while loop to calling DebugP_log() to print our memory buffer, the content of memory change abnormally.

I change the DebugP_log() to SBL_printf() but the issue is still there. The memory content still be altered randomly.

The memory content still be altered. I can't figure out why.

We use similar program and test with other application demo project. Here we use SPI loopback test for comparison.

Just import the SPI loopback test demo and replace the test code as attached file.

/*

* Copyright (C) 2021 Texas Instruments Incorporated

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

/* This example demonstrates the McSPI RX and TX operation configured

* in blocking, interrupt mode of operation.

*

* This example sends a known data in the TX mode of length APP_MCSPI_MSGSIZE

* and then receives the same in RX mode. Internal pad level loopback mode

* is enabled to receive data.

* To enable internal pad level loopback mode, D0 pin is configured to both

* TX Enable as well as RX input pin in the SYSCFG.

*

* When transfer is completed, TX and RX buffer data are compared.

* If data is matched, test result is passed otherwise failed.

*/

#include <kernel/dpl/DebugP.h>

#include <drivers/crc.h>

#include "ti_drivers_config.h"

#include "ti_drivers_open_close.h"

#include "ti_board_open_close.h"

// #define _MASTER_

/****************************/

/* BUFFER SIZE */

/****************************/

#define BUFFER_SIZE 128U

#define RXBUFFER_SIZE 128U

#define TXBUFFER_SIZE 128U

/****************************/

/* RX STATE */

/****************************/

#define FAIL 0x00

#define SUCCESS 0x01

#define NONE 0x02

/****************************/

/* ACK STATE */

/****************************/

#define ACK_FAIL 0x00

#define ACK_SUCCESS 0x01

#define ACK_RETRY 0x02

/****************************/

/* SEND STATE */

/****************************/

#define SEND_FAIL 0x00

#define SEND_SUCCESS 0x01

#define SEND_NONE 0x02

//#define SEND_RETRY 0x02

/****************************/

/* FW VERSION */

/****************************/

#define MAJOR_VER 0x00

#define MINOR_VER 0x00

#define TRIAL_VER 0x00

#define ADD_VER 0x01

/****************************/

/* MSG OFFSET */

/****************************/

#define SYNC_MSB_OFFSET 0

#define SYNC_LSB_OFFSET 1

/****************************/

/* MSG SYNC */

/****************************/

#define SYNC_MSB 0xAE

#define SYNC_LSB 0x86

/****************************/

/* PAYLOAD TYPE */

/****************************/

#define CMD 0x00

#define RESP 0x01

#define IND 0x02

/****************************/

/* POCKET */

/****************************/

#define PACKET_HDR_NUM 6

#define PACKET_CHKSUM_NUM 2

/****************************/

/* PAYLOAD LEN LIMIT */

/****************************/

#define PAYLOAD_LEN_MAX_CONTROL (RXBUFFER_SIZE - PACKET_HDR_NUM - PACKET_CHKSUM_NUM)

/* CRC configuration parameters */

#define APP_CRC_CHANNEL (CRC_CHANNEL_1)

/* CRC pattern size updated to 32 bits from 64 bits as CPU can copy only 32 bits at a time */

#define APP_CRC_SECT_CNT ((uint32_t) 1U)

#define APP_CRC_WATCHDOG_PRELOAD_VAL ((uint32_t) 0U)

#define APP_CRC_BLOCK_PRELOAD_VAL ((uint32_t) 0U)

#define APP_CRC_TYPE CRC_TYPE_16bit

#define APP_CRC_DATA_SIZE CRC_DW_16bit

#define APP_CRC_BIT_SWAP 0

#define APP_CRC_BYTE_SWAP 1

#define MSB_UINT16(x) (uint8_t)(x >> 8)

#define LSB_UINT16(x) (uint8_t)(x & 0xFF)

#define FIXED_POINT_SCALE (131072)

/****************************/

/* PROFILE */

/****************************/

typedef struct

{

uint16_t rx_size;

uint8_t rx_buffer[RXBUFFER_SIZE];

uint8_t tx_buffer[TXBUFFER_SIZE];

} PROFILE_STRUCT;

typedef struct

{

uint8_t sync_MSB;

uint8_t sync_LSB;

uint8_t seq_num;

uint8_t payload_type;

uint8_t payloadLen_MSB;

uint8_t payloadLen_LSB;

} packet_header_t;

typedef struct

{

uint8_t payload[BUFFER_SIZE - 11];

} dcu_command_t;

typedef struct

{

uint8_t payload[BUFFER_SIZE - 12];

} dcu_response_t;

typedef struct

{

uint8_t cmd_MSB;

uint8_t cmd_LSB;

uint8_t num_msg_bytes;

dcu_command_t dcu_cmd;

} tunnel_command_t;

typedef struct

{

uint8_t resp_MSB;

uint8_t resp_LSB;

uint8_t status_code;

uint8_t num_msg_bytes;

dcu_response_t dcu_response;

} tunnel_response_t;

typedef struct

{

uint32_t frame_header;

uint32_t tl;

uint32_t v;

} tunnel_indication_t;

typedef struct

{

packet_header_t header;

tunnel_command_t tunnel_command;

} command_t;

typedef struct

{

packet_header_t header;

tunnel_response_t tunnel_response;

} response_t;

typedef struct

{

packet_header_t header;

tunnel_indication_t tunnel_indication;

} indication_t;

int seq_num = 101;

PROFILE_STRUCT profile;

uint8_t ack_payload[3] = {0x00, 0xDE, 0x86};

uint8_t fw_version[6] = {MAJOR_VER, MINOR_VER, TRIAL_VER, ADD_VER, 0xDE, 0x86};

void UtilMoveLength(uint8_t *to_ptr, uint8_t *from_ptr, uint16_t size);

void MoveRxBufferUp(uint8_t size);

uint16_t CalcChecksum(uint8_t *tx_rx_buffer, uint16_t len);

void SPI_computeCrc16Cpu(uint16_t* data, uint32_t numbytes, uint16_t* crc16);

void MsgPresent(command_t **recvMsg);

void SendCommand(tunnel_command_t tunnel_command);

void SendResponse(tunnel_response_t tunnel_response);

void ProcResponse(uint8_t resp_MSB, uint8_t resp_LSB, uint8_t status_code, uint8_t num_msg_bytes, uint8_t *payload);

void SendIndication(tunnel_indication_t tunnel_indication);

uint8_t AckProcessor(void);

/*==============> UtilMoveLength <==============================*/

void UtilMoveLength(uint8_t *to_ptr, uint8_t *from_ptr, uint16_t size)

{

uint8_t *end_ptr;

/* calculate the end pointer */

end_ptr = to_ptr + size;

/* lets move length of the size */

for( ;to_ptr < end_ptr; to_ptr++)

{

*to_ptr = *from_ptr;

from_ptr++;

}

}

////////////////////////////////////////////////////////////////////////////////

// void MoveRxBufferUp(void)

////////////////////////////////////////////////////////////////////////////////

void MoveRxBufferUp(uint8_t size)

{

if (profile.rx_size >= size)

{

profile.rx_size -= size;

/* lets move the buffer up */

UtilMoveLength(&profile.rx_buffer[0], &profile.rx_buffer[size], profile.rx_size);

}

else

{

profile.rx_size = 0;

memset(profile.rx_buffer, 0, sizeof(profile.rx_buffer));

}

}

//uint16_t CalcChecksum(uint8_t *tx_rx_buffer, uint16_t len)

//{

// uint32_t loopCnt, baseAddr;

// CRC_Channel_t chNumber;

// CRC_Signature signVal;

// CRC_SignatureRegAddr psaSignRegAddr;

//

// /* Configure CRC parameters */

// baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

// chNumber = APP_CRC_CHANNEL;

//

// /* Get CRC PSA signature register address */

// CRC_getPSASigRegAddr(baseAddr, chNumber, &psaSignRegAddr);

//

// /* Initialize CRC channel */

// CRC_initialize(baseAddr, chNumber, APP_CRC_WATCHDOG_PRELOAD_VAL, APP_CRC_BLOCK_PRELOAD_VAL);

//

// CRC_configure(baseAddr, chNumber, len, APP_CRC_SECT_CNT, CRC_OPERATION_MODE_FULLCPU, APP_CRC_TYPE, APP_CRC_DATA_SIZE, APP_CRC_BIT_SWAP, APP_CRC_BYTE_SWAP);

//

// /* Reset the CRC channel*/

// CRC_channelReset(baseAddr, chNumber);

//

// /* compute the CRC by writing the data buffer on which CRC computation is needed */

// for (loopCnt = 0; loopCnt < len ; loopCnt++)

// {

// HW_WR_REG16(psaSignRegAddr.regL, tx_rx_buffer[loopCnt]);

// }

//

// /* Fetch CRC signature value */

// CRC_getPSASig(baseAddr, chNumber, &signVal);

//

// return signVal.regL;

//}

//void SPI_computeCrc16Cpu(uint16_t* data, uint32_t numbytes, uint16_t* crc16)

//{

// uint32_t loopCnt, patternCnt, baseAddr;

// CRC_Channel_t chNumber;

// CRC_SignatureRegAddr psaSignRegAddr;

// uint32_t app_crc_sect_cnt = 1U;

// uint32_t app_crc_watchdog_preload_val = 0U;

// uint32_t app_crc_block_preload_val = 0U;

// uint32_t app_crc_type = CRC_TYPE_16bit;

// uint32_t app_crc_data_size = CRC_DW_16bit;

// uint32_t app_crc_bit_swap = 1;

// uint32_t app_crc_byte_swap = 0;

// CRC_Signature calcrc;

//

// /* Configure CRC parameters */

// baseAddr = (uint32_t) AddrTranslateP_getLocalAddr(CONFIG_CRC0_BASE_ADDR);

// patternCnt = (numbytes / 2);

// chNumber = CRC_CHANNEL_2;

//

//

// /* Get CRC PSA signature register address */

// CRC_getPSASigRegAddr(baseAddr, chNumber, &psaSignRegAddr);

//

// /* Initialize and Configure CRC channel */

// CRC_initialize(baseAddr, chNumber, app_crc_watchdog_preload_val, app_crc_block_preload_val);

//

// CRC_configure(baseAddr, chNumber, patternCnt, app_crc_sect_cnt, CRC_OPERATION_MODE_FULLCPU, app_crc_type, app_crc_data_size ,app_crc_bit_swap, app_crc_byte_swap);

//

// /* Reset the CRC channel*/

// CRC_channelReset(baseAddr, chNumber);

//

// /* compute the CRC by writing the data buffer on which CRC computation is needed */

// for (loopCnt = 0; loopCnt < patternCnt ; loopCnt++)

// {

// HW_WR_REG16(psaSignRegAddr.regL, data[loopCnt]);

// }

//

// /* Fetch CRC signature value */

// CRC_getPSASig(baseAddr, chNumber, &calcrc);

// *crc16 = calcrc.regL;

// return;

//}

//

//void MsgPresent(command_t **recvMsg)

//{

// uint8_t status = FAIL;

// profile.rx_size = RXBUFFER_SIZE;

//

// while (profile.rx_size > 0)

// {

// /* Search Sync Bytes */

// if ((profile.rx_buffer[SYNC_MSB_OFFSET] != SYNC_MSB) ||

// (profile.rx_buffer[SYNC_LSB_OFFSET] != SYNC_LSB))

// {

// if (profile.rx_size == 1)

// {

// status = NONE;

// }

// MoveRxBufferUp(1);

// continue;

// }

//

// //check payload length

// packet_header_t *packetHeader = (packet_header_t *)profile.rx_buffer;

// uint16_t payloadLen = packetHeader->payloadLen_MSB << 8 | packetHeader->payloadLen_LSB;

//

// if (payloadLen >= PAYLOAD_LEN_MAX_CONTROL)

// {

// //get next packet

// MoveRxBufferUp(2);

// continue;

// }

//

// //verify checksum

// uint8_t checksumOffset = PACKET_HDR_NUM + payloadLen;

// uint16_t recvChecksum = profile.rx_buffer[checksumOffset] << 8 | profile.rx_buffer[checksumOffset + 1];

// uint16_t checksum;

// SPI_computeCrc16Cpu(&profile.rx_buffer, (PACKET_HDR_NUM + payloadLen), &checksum);

//

// if (recvChecksum != checksum)

// {

// //get next packet

// MoveRxBufferUp(2);

// continue;

// }

//

// //Packet correct, return packet

// status = SUCCESS;

// break;

// }

//// uint8_t *payload = &((*recvMsg)->tunnel_command);

// if (status == SUCCESS)

// {

// *recvMsg = (command_t *)profile.rx_buffer;

// if ((*recvMsg)->tunnel_command.cmd_LSB == 0x36)

// {

// ProcResponse(0x00, 0x00, ACK_SUCCESS, 0x04, fw_version);

// }

// else

// {

// ProcResponse(0x00, 0x00, ACK_SUCCESS, 0x01, ack_payload);

// }

// }

//

// else if (status == FAIL)

// {

// ProcResponse(0x00, 0x00, ACK_FAIL, 0x01, ack_payload);

// }

//}

//

//void SendCommand(tunnel_command_t tunnel_command)

//{

// int i;

// uint16_t payloadLen = 3;

// command_t command = {0};

//

// //header

// command.header.sync_MSB = SYNC_MSB;

// command.header.sync_LSB = SYNC_LSB;

// command.header.seq_num = seq_num++;

// command.header.payload_type = CMD;

//

// for (i = 0; i < sizeof(tunnel_command.dcu_cmd.payload); i++)

// {

// if (tunnel_command.dcu_cmd.payload[i] == 0xCE && tunnel_command.dcu_cmd.payload[i + 1] == 0x86)

// {

// break;

// }

//

// payloadLen++;

// }

//

// command.header.payloadLen_MSB = MSB_UINT16(payloadLen);

// command.header.payloadLen_LSB = LSB_UINT16(payloadLen);

//

// //tunnel command

// command.tunnel_command.cmd_MSB = tunnel_command.cmd_MSB;

// command.tunnel_command.cmd_LSB = tunnel_command.cmd_LSB;

// command.tunnel_command.num_msg_bytes = tunnel_command.num_msg_bytes;

// memcpy(&command.tunnel_command.dcu_cmd.payload, &tunnel_command.dcu_cmd.payload, payloadLen);

//

// //push command to TX buffer

// memset(&profile.tx_buffer, 0, TXBUFFER_SIZE);

// uint16_t checksumOffset = PACKET_HDR_NUM + payloadLen;

// memcpy(&profile.tx_buffer, &command, checksumOffset);

//

// //checksum

// uint16_t checksum;

// SPI_computeCrc16Cpu(profile.tx_buffer, checksumOffset, &checksum);

// profile.tx_buffer[checksumOffset] = MSB_UINT16(checksum);

// profile.tx_buffer[checksumOffset + 1] = LSB_UINT16(checksum);

//}

//

//void SendResponse(tunnel_response_t tunnel_response)

//{

// int i;

// uint16_t payloadLen = 4;

// response_t response = {0};

//

// response.header.sync_MSB = SYNC_MSB;

// response.header.sync_LSB = SYNC_LSB;

// response.header.seq_num = seq_num++;

// response.header.payload_type = RESP;

//

// for (i = 0; i < sizeof(tunnel_response.dcu_response.payload); i++)

// {

// if (tunnel_response.dcu_response.payload[i] == 0xDE && tunnel_response.dcu_response.payload[i + 1] == 0x86)

// {

// break;

// }

// payloadLen++;

// }

//

// response.header.payloadLen_MSB = MSB_UINT16(payloadLen);

// response.header.payloadLen_LSB = LSB_UINT16(payloadLen);

//

// //tunnel response

// response.tunnel_response.resp_MSB = tunnel_response.resp_MSB;

// response.tunnel_response.resp_LSB = tunnel_response.resp_LSB;

// response.tunnel_response.status_code = tunnel_response.status_code;

// response.tunnel_response.num_msg_bytes = tunnel_response.num_msg_bytes;

// memcpy(&response.tunnel_response.dcu_response.payload, &tunnel_response.dcu_response.payload, payloadLen);

//

// //push response to TX buffer

// memset(&profile.tx_buffer, 0, TXBUFFER_SIZE);

// uint16_t checksumOffset = PACKET_HDR_NUM + payloadLen;

// memcpy(&profile.tx_buffer, &response, checksumOffset);

//

// //checksum

// uint16_t checksum;

// SPI_computeCrc16Cpu(profile.tx_buffer, checksumOffset, &checksum);

// profile.tx_buffer[checksumOffset] = MSB_UINT16(checksum);

// profile.tx_buffer[checksumOffset + 1] = LSB_UINT16(checksum);

//}

//

//////////////////////////////////////////////////////////////////////////////////

//// ProcResponse(uint8_t resp_MSB, uint8_t resp_LSB, uint8_t status_code, uint8_t num_msg_bytes, uint8_t *payload)

//////////////////////////////////////////////////////////////////////////////////

//void ProcResponse(uint8_t resp_MSB, uint8_t resp_LSB, uint8_t status_code, uint8_t num_msg_bytes, uint8_t *payload)

//{

// tunnel_response_t tunnel_response = {0};

//

// //make dcu response

// tunnel_response.resp_MSB = resp_MSB;

// tunnel_response.resp_LSB = resp_LSB;

// tunnel_response.status_code = status_code;

// tunnel_response.num_msg_bytes = num_msg_bytes;

//// tunnel_response.dcu_response.payload[0] = 0x00;

//// tunnel_response.dcu_response.payload[1] = 0xDE;

//// tunnel_response.dcu_response.payload[2] = 0x86;

// memcpy(tunnel_response.dcu_response.payload, payload, num_msg_bytes + 2);

//

// //send response

// SendResponse(tunnel_response);

//}

//

//void SendIndication(tunnel_indication_t tunnel_indication)

//{

//

// int i;

// indication_t indication = {0};

//

// //header

// indication.header.sync_MSB = SYNC_MSB;

// indication.header.sync_LSB = SYNC_LSB;

//

// indication.header.payload_type = IND;

//

// uint16_t payloadLen = sizeof(tunnel_indication);

// indication.header.payloadLen_MSB = MSB_UINT16(payloadLen);

// indication.header.payloadLen_LSB = LSB_UINT16(payloadLen);

//

// //tunnel indication

// memcpy(&indication.tunnel_indication, &tunnel_indication, sizeof(tunnel_indication));

//

// //push indication to TX buffer

// memset(&profile.tx_buffer, 0, TXBUFFER_SIZE);

// uint16_t checksumOffset = PACKET_HDR_NUM + payloadLen;

// memcpy(&profile.tx_buffer, &indication, checksumOffset);

//

// //checksum

// uint16_t checksum = CalcChecksum(profile.tx_buffer, checksumOffset);

// profile.tx_buffer[checksumOffset] = MSB_UINT16(checksum);

// profile.tx_buffer[checksumOffset + 1] = LSB_UINT16(checksum);

//}

//

//uint8_t AckProcessor(void)

//{

// response_t *response = (response_t *)profile.rx_buffer;

//

// if (response->tunnel_response.status_code == ACK_SUCCESS)

// {

// return SEND_SUCCESS;

// }

// else if (response->tunnel_response.status_code == ACK_FAIL)

// {

// return SEND_FAIL;

// }

//

// return SEND_NONE;

//}

//

//static void CLI_QformatToFloat(float *a_floatvalue, uint32_t a_Qvalue)

//{

// uint8_t sign_flag = 0U;

// float f_val;

//

// sign_flag = (a_Qvalue & (1 << 31)) >> 31; // the get sign bit at MSB

// f_val = ((float)(a_Qvalue & 0x7FFFFFFF) / FIXED_POINT_SCALE);

//

// if (sign_flag)

// {

// *a_floatvalue = f_val*(-1.0);

// }

// else

// {

// *a_floatvalue = f_val;

// }

//}

//

//static void CLI_FloatToQformat(uint32_t *a_Qvalue, float a_floatvalue)

//{

// uint32_t Q_val = 0U;

//

// if (a_floatvalue < 0)

// {

// Q_val =(uint32_t)(a_floatvalue * (-1.0) * FIXED_POINT_SCALE);

// *a_Qvalue = Q_val | (1 << 31);

// }

// else

// {

// Q_val =(uint32_t)(a_floatvalue * FIXED_POINT_SCALE);

// *a_Qvalue = Q_val;

// }

//}

//

//static void CLI_IntToQformat(uint32_t *a_Qvalue, int a_intvalue)

//{

// uint32_t Q_val = 0U;

//

// if (a_intvalue < 0)

// {

// Q_val = (uint32_t)(a_intvalue * (-1));

// *a_Qvalue = Q_val | (1 << 31);

// }

// else

// {

// *a_Qvalue = Q_val;

// }

//}

//

//static void CLI_QformatToInt(int *a_intvalue, uint32_t a_Qvalue)

//{

// uint8_t sign_flag = 0U;

// sign_flag = (a_Qvalue & (1 << 31)) >> 31; // the get sign bit at MSB

//

// if(sign_flag)

// {

// *a_intvalue = ((int)(a_Qvalue & 0x7FFFFFFF))*(-1);

// }

// else

// {

// *a_intvalue = (int)(a_Qvalue & 0x7FFFFFFF);

// }

//}

#define HEAD_SYMBOL_NUMBER (3)

#define HEAD_BUFFER_SYSTEM (0)

#define FLASH_RWBUFFER_SIZE (24)

#define HEAD_SYMBOL_SYSTEM 'TDYS'

uint8_t gFlashModifyBuffer[HEAD_SYMBOL_NUMBER][FLASH_RWBUFFER_SIZE];

typedef struct CLI_confighead_t

{

/**

* @brief Configuration which was used to configure the CLI module

*/

uint32_t head_symbol;

/**

* @brief This is the number of CLI commands which have been added to the module

*/

uint32_t section_numbers;

/**

* @brief This is the number of CLI commands which have been added to the module

*/

uint32_t section_size_byte;

}CLI_confighead;

uint32_t command_buff[4];

void *mcspi_loopback_main(void *args)

{

int32_t status = SystemP_SUCCESS;

uint32_t i, j;

int32_t transferOK;

MCSPI_Transaction spiTransaction;

uint64_t startTimeInUSec, elapsedTimeInUsecs;

uint32_t Qvalue;

Drivers_open();

Board_driversOpen();

DebugP_log("[MCSPI] Loopback example started ...\r\n");

uint32_t read_position = 0U;

uint32_t size = 0U;

uint32_t cnt = 0U;

// uint16_t CRC_cal;

CLI_confighead confighead;

size = sizeof(confighead);

read_position = read_position + size;

size = sizeof(uint32_t) * 4;

command_buff[0] = size - sizeof(uint32_t) ; //section size

command_buff[1] = 0;

command_buff[2] = 0;

command_buff[3] = 0xb;

memcpy(gFlashModifyBuffer[HEAD_BUFFER_SYSTEM] + read_position, command_buff, size);

read_position = read_position + size;

cnt++;

confighead.head_symbol = (uint32_t)HEAD_SYMBOL_SYSTEM;

confighead.section_numbers = cnt;

confighead.section_size_byte = read_position;

memcpy((uint8_t*)gFlashModifyBuffer[HEAD_BUFFER_SYSTEM], (uint8_t*)&confighead, sizeof(confighead));

DebugP_log("\r\nHEAD_SYMBOL_SYSTEM: %x\r\n", HEAD_SYMBOL_SYSTEM);

DebugP_log("HEAD_SYMBOL_SYSTEM (BUFFER) (After memcpy):");

// uint32_t i;

for (i = 0; i < 28; i++)

{

DebugP_log("%x ", gFlashModifyBuffer[HEAD_BUFFER_SYSTEM][i]);

}

DebugP_log("\r\n");

while(1);

// /* Initiate transfer */

// MCSPI_Transaction_init(&spiTransaction);

// spiTransaction.channel = gConfigMcspi0ChCfg[0].chNum;

// spiTransaction.dataSize = 8;

// spiTransaction.csDisable = TRUE;

// spiTransaction.count = BUFFER_SIZE / (spiTransaction.dataSize/8);

// spiTransaction.txBuf = (void *)(profile.tx_buffer);

// spiTransaction.rxBuf = (void *)(profile.rx_buffer);

// spiTransaction.args = NULL;

//

// DebugP_log("[MCSPI] Loopback example started ...\r\n");

//

// /* Memfill buffers */

// tunnel_command_t tunnel_command = {0};

// tunnel_command.cmd_MSB = 0x00;

// tunnel_command.cmd_LSB = 0x36;

// tunnel_command.num_msg_bytes = 0x01;

// tunnel_command.dcu_cmd.payload[0] = 0x01;

// tunnel_command.dcu_cmd.payload[1] = 0xCE;

// tunnel_command.dcu_cmd.payload[2] = 0x86;

//

//// uint32_t t0[32] = {0};

////

//// t0[0] = 1;

//// CLI_FloatToQformat(&Qvalue, 1.2);

//// t0[1] = Qvalue;

//// CLI_FloatToQformat(&Qvalue, 0.2);

//// t0[2] = Qvalue;

//// t0[3] = 0x0000CE86;

////

//// tunnel_command_t tunnel_command0 = {0};

//// tunnel_command0.cmd_MSB = 0;

//// tunnel_command0.cmd_LSB = 18;

//// tunnel_command0.num_msg_bytes = 12;

//// memcpy(&tunnel_command0.dcu_cmd.payload, &t0, sizeof(t0));

//

//// uint32_t t1[32] = {0};

////

//// t1[0] = 7;

//// t1[1] = 3;

//// t1[2] = 0x0000CE86;

////

//// tunnel_command_t tunnel_command1 = {0};

//// tunnel_command1.cmd_MSB = 0;

//// tunnel_command1.cmd_LSB = 4;

//// tunnel_command1.num_msg_bytes = 12;

//// memcpy(&tunnel_command1.dcu_cmd.payload, &t1, sizeof(t1));

////

//// uint32_t t2[32] = {0};

////

//// t2[0] = 8;

//// t2[1] = 0;

//// t2[2] = 0;

//// t2[3] = 256;

//// t2[4] = 1;

//// t2[5] = 51;

//// t2[6] = 0;

//// t2[7] = 0x0000CE86;

////

//// tunnel_command_t tunnel_command2 = {0};

//// tunnel_command2.cmd_MSB = 0;

//// tunnel_command2.cmd_LSB = 5;

//// tunnel_command2.num_msg_bytes = 28;

//// tunnel_command2.dcu_cmd.payload;

//// memcpy(&tunnel_command2.dcu_cmd.payload, &t2, sizeof(t2));

////

//// uint32_t t3[32] = {0};

////

//// t3[0] = 16;

//// t3[1] = 8;

//// t3[2] = 1;

//// t3[3] = 2;

//// t3[4] = 4;

//// t3[5] = 4;

//// t3[6] = 0;

//// t3[7] = 15;

//// t3[8] = 0x0000CE86;

////

//// tunnel_command_t tunnel_command3 = {0};

//// tunnel_command3.cmd_MSB = 0;

//// tunnel_command3.cmd_LSB = 11;

//// tunnel_command3.num_msg_bytes = 32;

//// memcpy(&tunnel_command3.dcu_cmd.payload, &t3, sizeof(t3));

////

//// uint32_t t4[32] = {0};

////

//// t4[0] = 0;

//// t4[1] = 0x0000CE86;

////

//// tunnel_command_t tunnel_command4 = {0};

//// tunnel_command4.cmd_MSB = 0;

//// tunnel_command4.cmd_LSB = 15;

//// tunnel_command4.num_msg_bytes = 4;

//// memcpy(&tunnel_command4.dcu_cmd.payload, &t4, sizeof(t4));

////

//// uint32_t t5[32] = {0};

////

//// t5[0] = 0;

//// t5[1] = 0;

//// t5[2] = 0;

//// t5[3] = 0;

//// t5[4] = 0x0000CE86;

////

//// tunnel_command_t tunnel_command5 = {0};

//// tunnel_command5.cmd_MSB = 0;

//// tunnel_command5.cmd_LSB = 2;

//// tunnel_command5.num_msg_bytes = 16;

//// memcpy(&tunnel_command5.dcu_cmd.payload, &t5, sizeof(t5));

//

// while (1)

// {

// SendCommand(tunnel_command);

//

// memset(&profile.rx_buffer, 0U, RXBUFFER_SIZE);

//

//#ifdef _MASTER_

// DebugP_log("[Master] wait for 1 s ...\r\n");

// ClockP_usleep(1000 * 1000);

//#endif

// ClockP_usleep(1000 * 1000); // 1s

//

// /* Print Tx data */

//#ifdef _MASTER_

// DebugP_log("[Master] Tx Data:\r\n");

//#else

// DebugP_log("[Slave] Tx Data:\r\n");

//#endif

//// for(i = 0U; i < TXBUFFER_SIZE; i++)

//// {

//// DebugP_log("%X ", profile.tx_buffer[i]);

//// }

//

//// SendCommand(tunnel_command0);

// for(i = 0U; i < TXBUFFER_SIZE; i++)

// {

// DebugP_log("%X ", profile.tx_buffer[i]);

// }

// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

// for(i = 0U; i < TXBUFFER_SIZE; i++)

// {

// DebugP_log("%X ", profile.tx_buffer[i]);

// }

// command_t *recvMsg0 = NULL;

// MsgPresent(&recvMsg0);

// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

// for(i = 0U; i < TXBUFFER_SIZE; i++)

// {

// DebugP_log("%X ", profile.tx_buffer[i]);

// }

// AckProcessor();

//

// for(i = 0U; i < TXBUFFER_SIZE; i++)

// {

// DebugP_log("%X ", profile.tx_buffer[i]);

// }

//

//// SendCommand(tunnel_command1);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// command_t *recvMsg1 = NULL;

//// MsgPresent(&recvMsg1);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// AckProcessor();

////

//// for(i = 0U; i < TXBUFFER_SIZE; i++)

//// {

//// DebugP_log("%X ", profile.tx_buffer[i]);

//// }

////

//// SendCommand(tunnel_command2);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// command_t *recvMsg2 = NULL;

//// MsgPresent(&recvMsg2);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// AckProcessor();

////

//// for(i = 0U; i < TXBUFFER_SIZE; i++)

//// {

//// DebugP_log("%X ", profile.tx_buffer[i]);

//// }

////

//// SendCommand(tunnel_command3);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// command_t *recvMsg3 = NULL;

//// MsgPresent(&recvMsg3);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// AckProcessor();

////

//// for(i = 0U; i < TXBUFFER_SIZE; i++)

//// {

//// DebugP_log("%X ", profile.tx_buffer[i]);

//// }

////

//// SendCommand(tunnel_command4);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// command_t *recvMsg4 = NULL;

//// MsgPresent(&recvMsg4);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// AckProcessor();

////

//// for(i = 0U; i < TXBUFFER_SIZE; i++)

//// {

//// DebugP_log("%X ", profile.tx_buffer[i]);

//// }

////

//// SendCommand(tunnel_command5);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// command_t *recvMsg5 = NULL;

//// MsgPresent(&recvMsg5);

//// MCSPI_transfer(gMcspiHandle[CONFIG_MCSPI0], &spiTransaction);

//// AckProcessor();

////

//// for(i = 0U; i < TXBUFFER_SIZE; i++)

//// {

//// DebugP_log("%X ", profile.tx_buffer[i]);

//// }

//

// elapsedTimeInUsecs = ClockP_getTimeUsec() - startTimeInUSec;

//

//#ifdef _MASTER_

// DebugP_log("I'm Master device\r\n");

//#else

// DebugP_log("I'm Slave device\r\n");

//#endif

// DebugP_log("----------------------------------------------------------\r\n");

// DebugP_log("McSPI Clock %d Hz\r\n", gConfigMcspi0ChCfg[0U].bitRate);

// DebugP_log("----------------------------------------------------------\r\n");

// DebugP_log("Data Width \tData Length \tTransfer Time (micro sec)\r\n");

// DebugP_log("%u\t\t%u\t\t%5.2f\r\n", spiTransaction.dataSize, BUFFER_SIZE,

// (float)elapsedTimeInUsecs);

// DebugP_log("----------------------------------------------------------\r\n\n");

//

// /* Print Rx data */

//#ifdef _MASTER_

// DebugP_log("[Master] Received Data:\r\n");

//#else

// DebugP_log("[Slave] Received Data:\r\n");

//#endif

//

// for(i = 0U; i < RXBUFFER_SIZE; i++)

// {

// DebugP_log("%X ", profile.rx_buffer[i]);

// }

// }

Board_driversClose();

Drivers_close();

return NULL;

}

The result is correct.

The issue only appears when we use SBL demo project.

May I have your help to check what happens?

Regards

Andre