Hello, please tell me about the SPI response of PGA970 EVM.

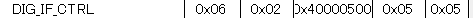

I am trying to read the DIGI_IF_CTRL register (DI PAGE2/OFFSET6) in a test to perform SPI communication with the PGA970.

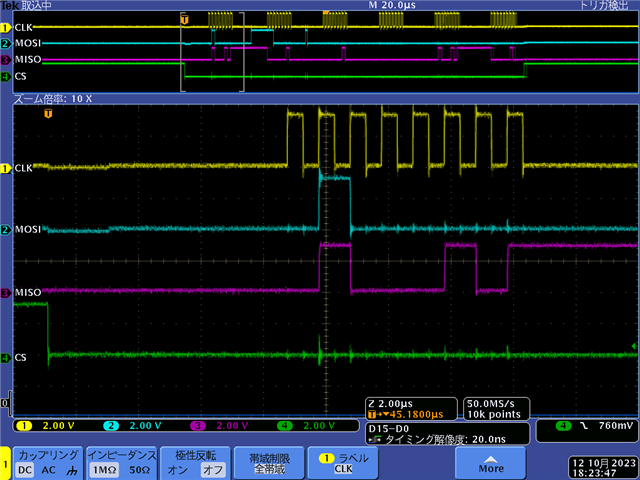

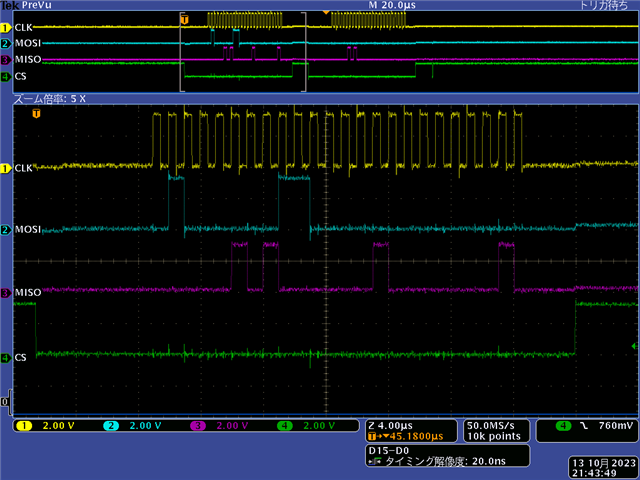

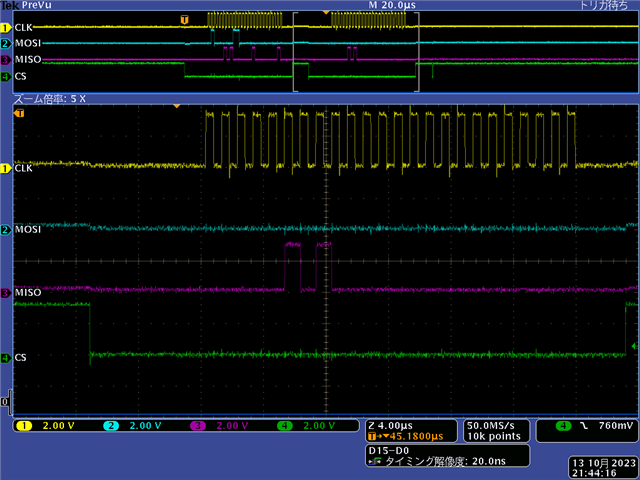

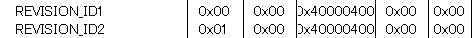

I sent 6 bytes of 40:C0:00:00:00:00, and the data I received instead was 45:02:02:00:45:02.

The 4th byte was 0x00, not 0x05. The 0x05 response in Figure 34 on page 42 of slds201.pdf is

I couldn't get it.

I checked to see if SPI_EN was set, but when I looked at it with the GUI tool, it was set.

e2e.ti.com/.../pga970-enabling-spi-without-internal-mcu

But it was mentioned as being enabled by default.

How can I get a 0x05 response?

Also, PGA970_Generic_Firmware_Installer.zip contains the SPI function library source file.

I don't think so. Do you have any samples for using SPI?