Other Parts Discussed in Thread: , UNIFLASH

Greetings,

We are developing a product and have an issue with running firmware on a custom pcb with the IWR6843AOP chip.

The hardware is the same as the IWR6843AOPEVM, except it is stripped down of all excess (no bluetooth chip, SOP switches, USB connectors etc).

Only the IWR6843AOP, Crystal (CX2016DB40000D0FLJCC), Spi flash (MX25R1635FZUIH0) and a Power Management IC (LP87524JRNFRQ1) are placed.

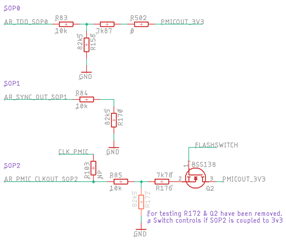

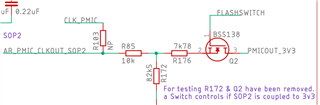

The Power management, decoupling, SOP pins, and other Pull-up's & Down's are copied from the Development kit (IWR6843AOPEVM schematics & Layout).

When testing the PCB we followed the hardware implementation excel document (www.ti.com/.../swrr161) and found a problem when checking T3-9

"Measure the voltages on the "1p4V_APLL" and 1p4V_SYNTH" pins". Pin 1.4V_SYNTH does not have 1.4V, if I am correct this pin won't be high until the application is running and RF frontend started. So, why won't that happen?

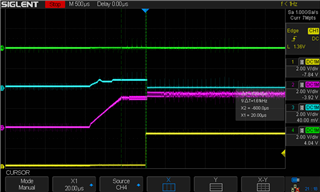

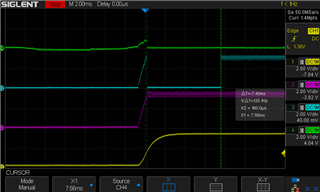

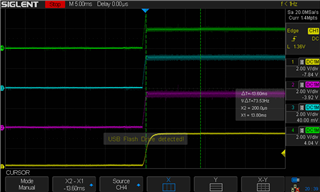

When going further we were able to flash the out of box demo (from IWR6843AOPEVM) with Uniflash (SOP2 set to logic "1", flashing after reset). Programming works the first time the device is powered on. The second time it does not work, but if we turn off the device for a minute it works again.

After succesful flashing SOP2 is set to logic "0" and the power is cycled. If we now sent commands to the flashing UART we receive an echo of the sent command.

The baudrate is 57.6k sending and receiving, other baudrates do not work. I would expect to be talking to the CLI that is implemented in the firmware, but this is not the case.

Some Hardware information:

SOP0 - Pulled to logic "1";

SOP1 - Pulled to logic "0" measures 0V;

SOP2 - Switchable between logic "1" and "0", measured 0V and 1.85V (according to datasheet it needs to be above 1.57v to be registered as logic "1").

Power is OK, the voltages are:

- 1.0V;

- 1.2V;

- 1.8V;

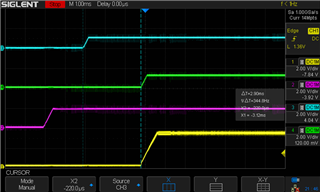

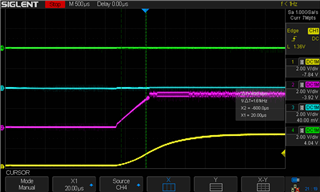

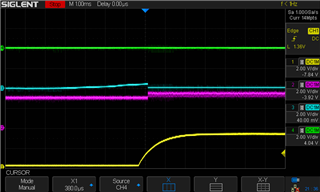

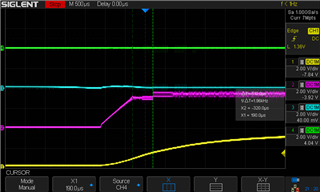

- 3.3V, this VIO voltage does have a slight ripple.

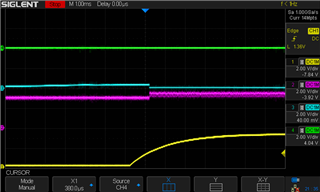

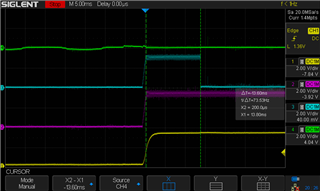

When measuring crystal oscilating frequency we see 40MHz.

JTAG is added to this board, tested quickly but did not work.

We did not document this process, it was quick and we should try this again.

Some findings

- SPI Flash is programmed at 80MHz, I would expect 40MHz.

- In order to boot in functional mode or flash mode the device needs to be powered off for 1 minute.

Kind regards,

Yves