Hi,

I'm trying to use Magnitude Squared Mode in Complex Multiplication.

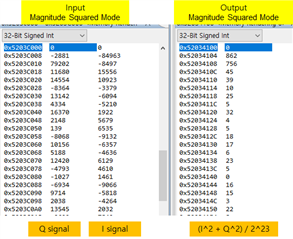

However, the output is dropped by 23 bits.

Can I control drop bit?

If it is possible, please guide me.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

Which example are you working with? Could you provide the modifications you made as well?

Thanks,

Clinton

Hi,

I am implementing autocorrelation about real-signal using FFT.

The procedure is as follows:

step1. FFT

step2. x * conj(x) <<- apply Magnitude Squared Mode

step3..FFT

step2 HWA configuration :

srcscale : 0

dstscale : 8

butterflyscaling : 0

Result is below:

Thanks.

Sincerely.

Hi,

Thanks for providing the details. If you could point out where in the code you are performing your configuration and calculations, that would be helpful too.

In the meantime, have you had a chance to look through our Radar Hardware Accelerator User's Guide? It can be found here:

https://www.ti.com/lit/pdf/swru526

Thanks,

Clinton

hi.

I already have the document, and it was implemented based on the documents.

However, there is no information about bit loss and control method of Magnitude Squared Mode in the document.

Could you find it for me?

Thanks.

Sincerely.

Hi,

I'm working to find more information on this. I will provide an update in the next day or so.

Thanks,

Clinton

Hi,

We cannot control the dropped bits. Yes, it is equivalent to x*x’/223 .

One option is to scale up the input so that it occupies the left most position in the 24 bit word. We would need to know what is the maximum signal level. For example, if the input is 16 bits we can put it in the upper 2 bytes (srcScale = 0), or if it is 32 bit and we know that the values do not exceed 24 bits we can put it to 24 bit input without shift (srcScale=0).

Thanks,

Clinton