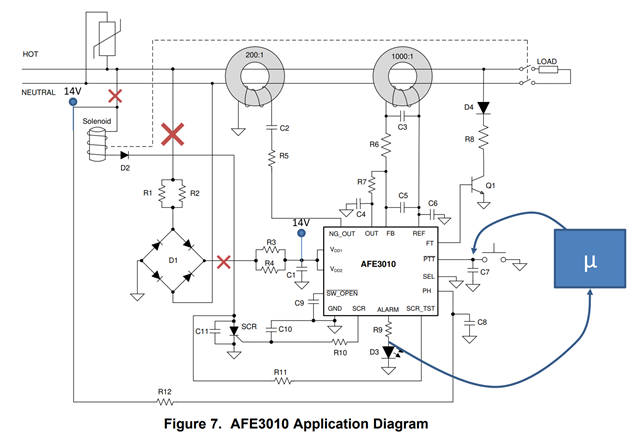

Does AFE3010 operate normally if all connections to the line are interrupted? The power for the AFE3010, shown in the diagram as a 14VDC source, would come from the cold side, where the microcontroller unit sits. The only connection to the power line would be isolated through the current transformers. Below is a rudimentary diagram. Red crosses show where connections are eliminated:

The idea is to save cost in the system by reducing the number of optoisolators. Can you please comment?

Thank you!