Other Parts Discussed in Thread: AWR2944

Hi

I have some questions about the TCMA and the TCMB:

Background:

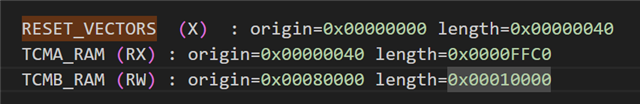

The link.cmd in the SDK (mmwave_mcuplus_sdk_04_04_01_02\ti\platform\awr2944\r5f_linker_enet.cmd) shown in the below picture:

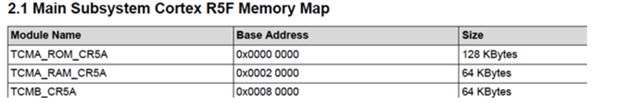

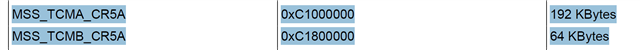

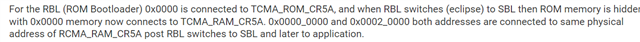

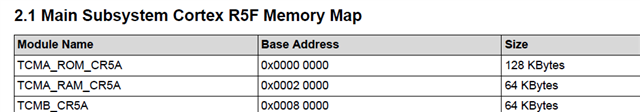

a. Does the section of RESET_VECTORS and TCMA_RAM belong to the TCMA_ROM_CR5A?

b. What does the TCMA_RAM use for?

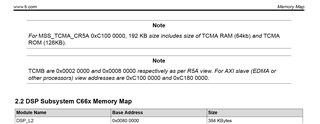

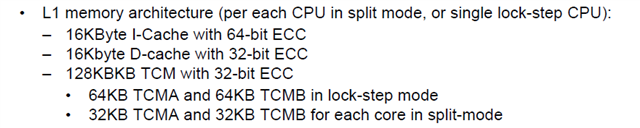

c. And has the R5F_RBL been put this area(TCMA_RAM), because the TCMA_ROM_CR5A size is 128KB, but the sum size of the RESET_VECTORS and TCMA_RAM is only 64KB.

d. TCMB_RAM size is 64KB, does that means the CPU of the SDK demo is in lock-step mode?

e. But why do not we use the TCMA_RAM_CR5A?

BR

Sonia Yang