Part Number: AFE3010

Dear Peter,

Here I have some questions about AFE3010 application as below,

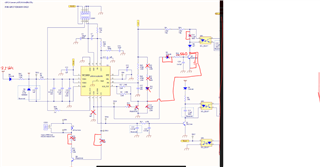

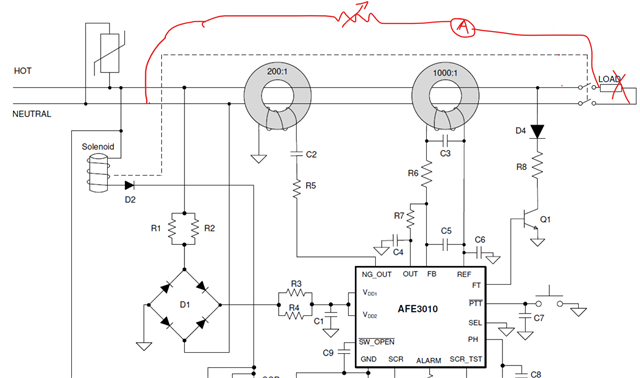

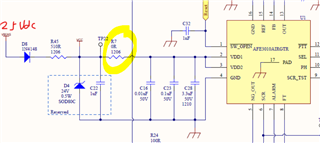

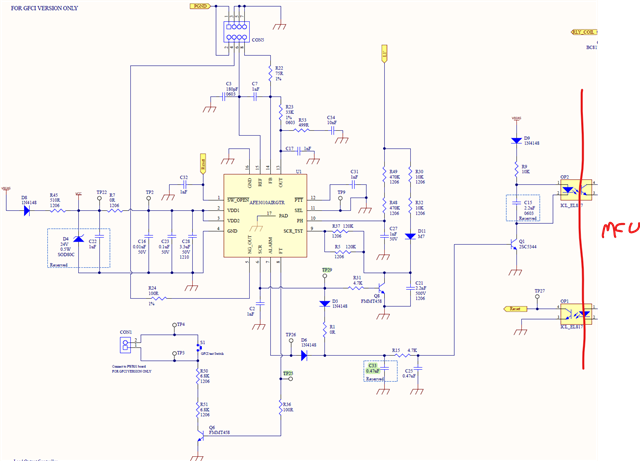

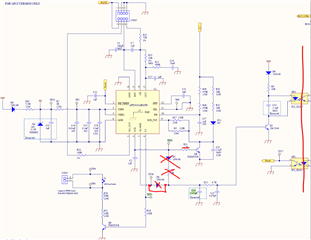

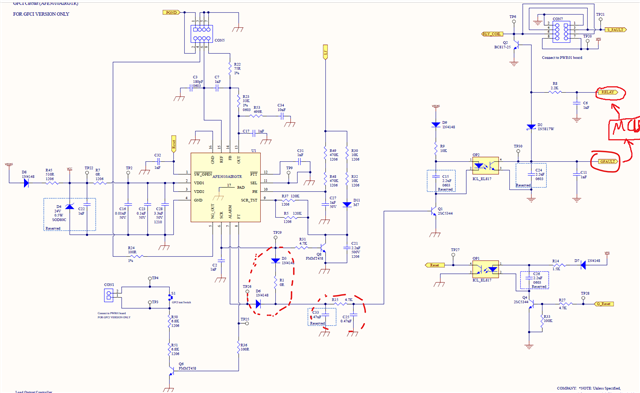

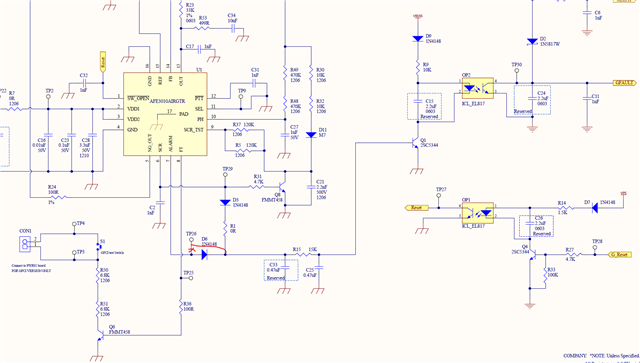

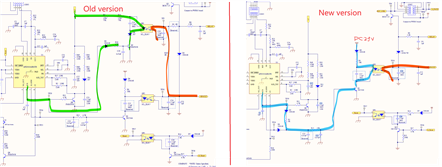

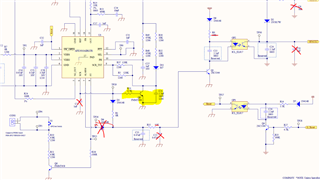

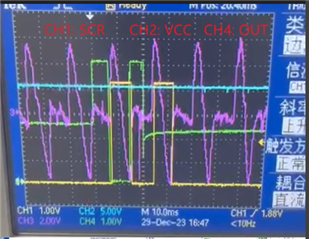

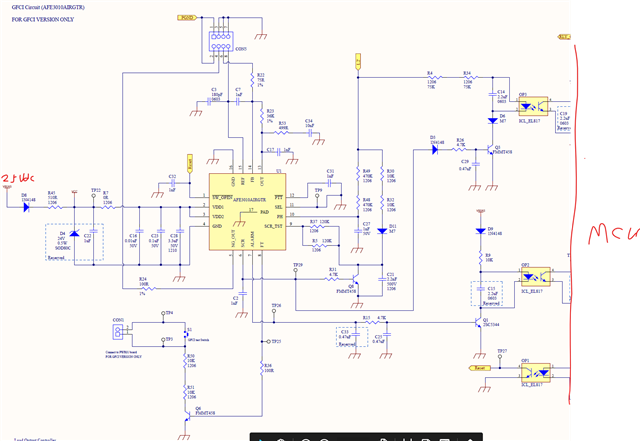

The circuitry as below,main function inclued EOL & GFAULT,

Questions:

1. Any comements/suggestions on SCR-TST external connection? Will it affect SCR self test ?

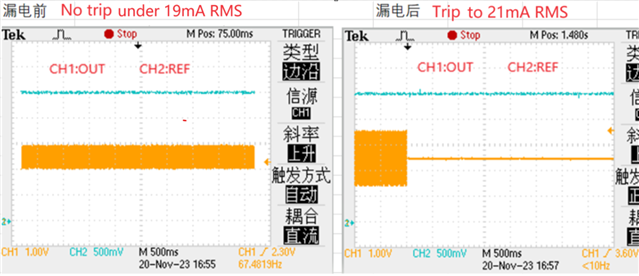

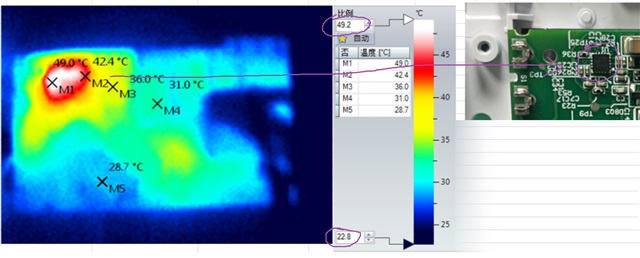

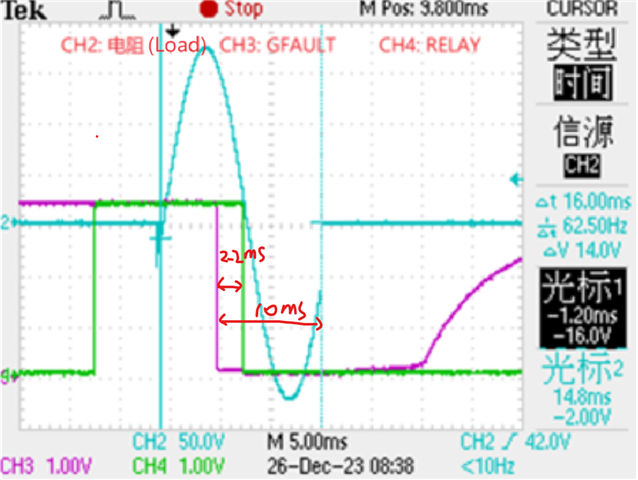

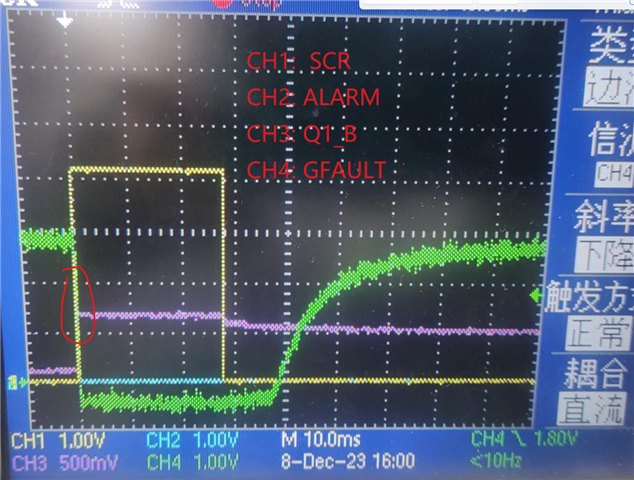

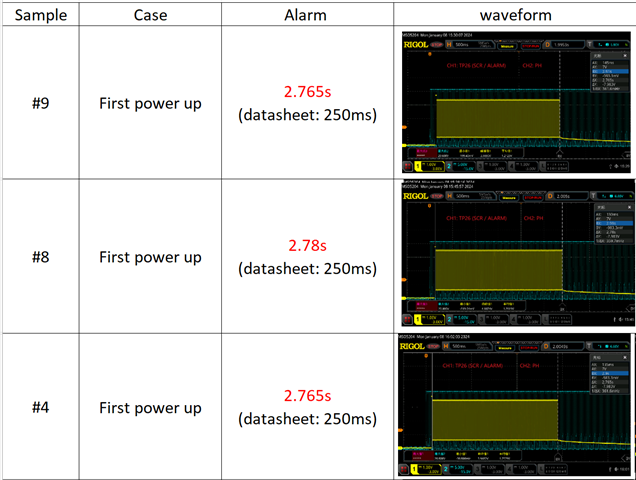

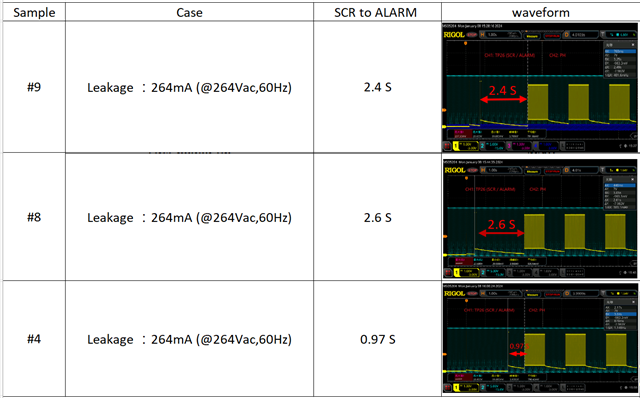

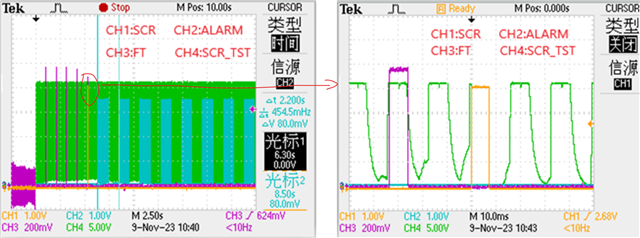

2. Power on by 120Vac 60Hz or 230Vac 60Hz, the ALARM output High(0.5Hz). We did below test, pls check and advise your idea.

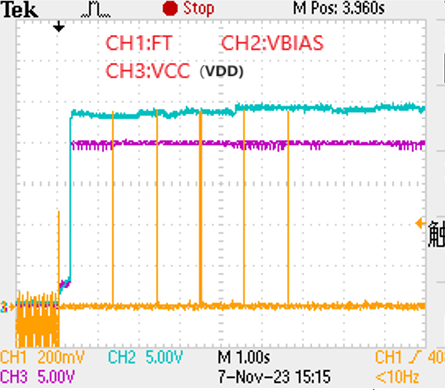

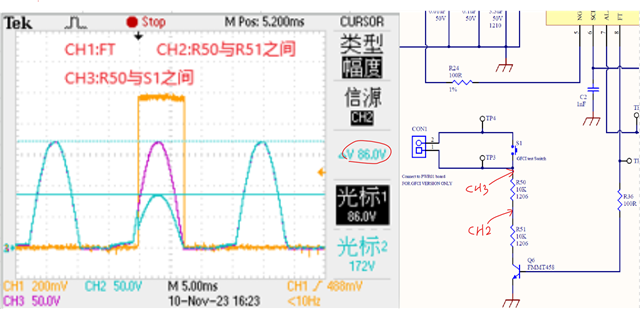

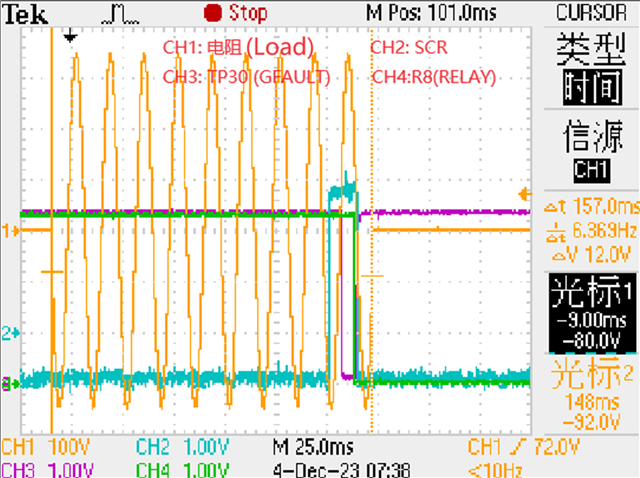

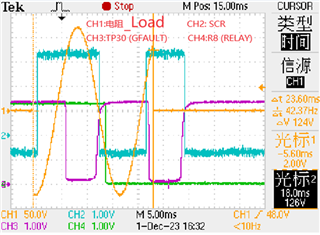

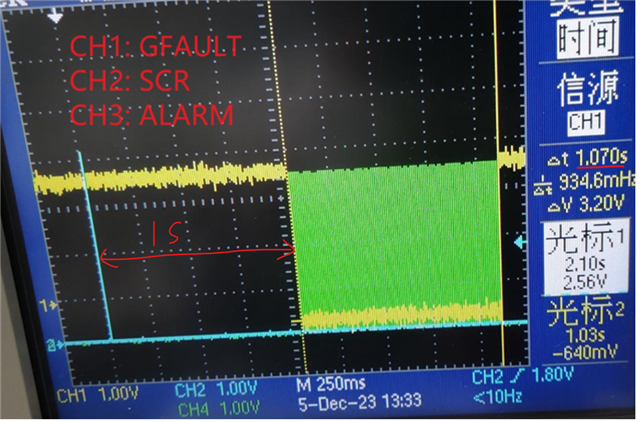

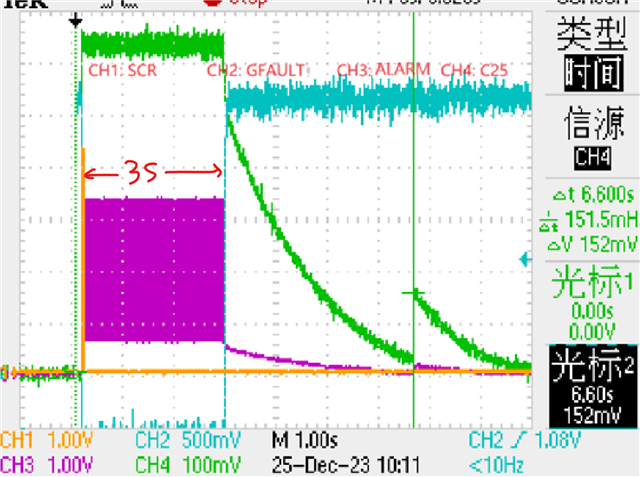

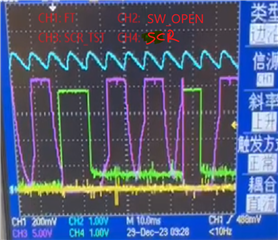

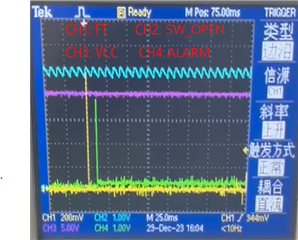

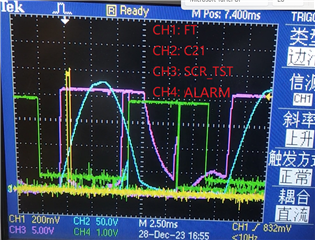

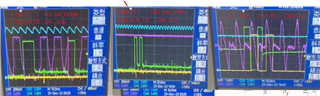

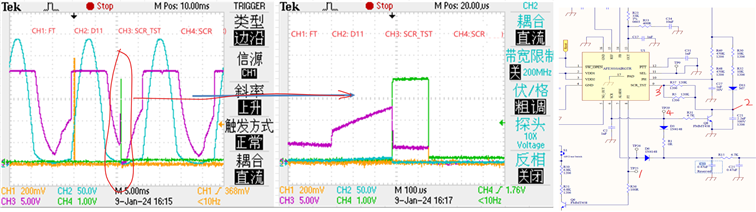

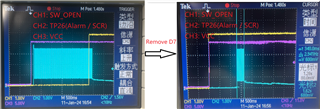

a. SCR,ALARM,FT, SCR_TST wave while power on 120Vac,60Hz:

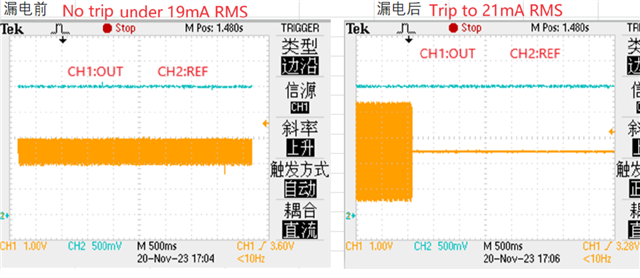

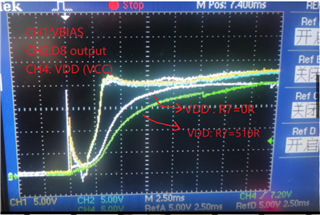

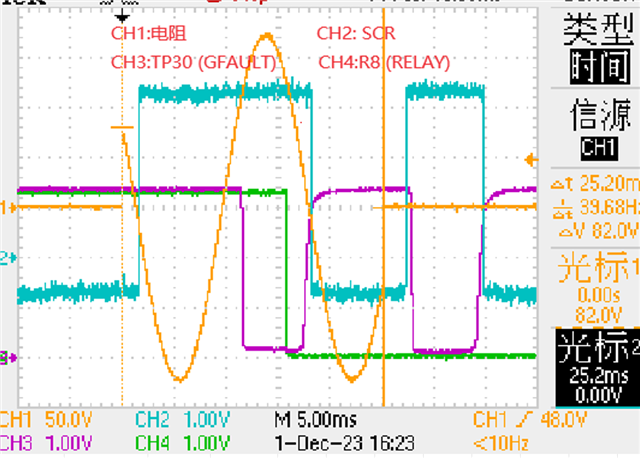

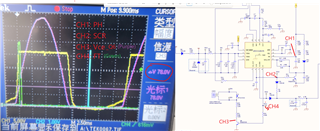

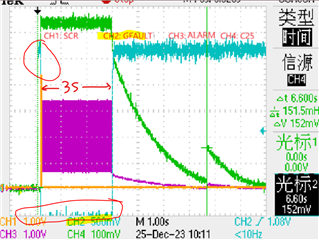

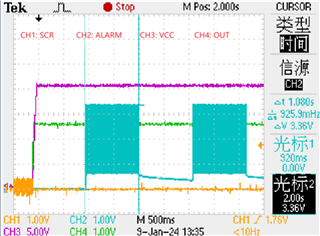

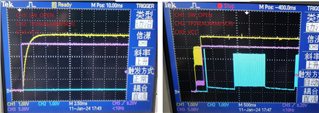

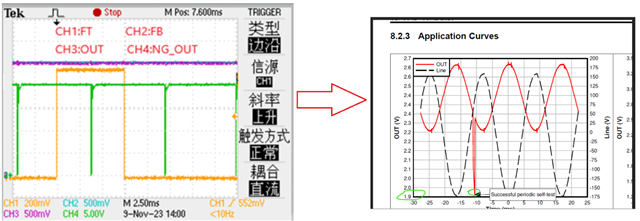

b. OUT wave is different from datasheet figure 17

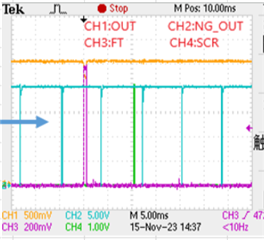

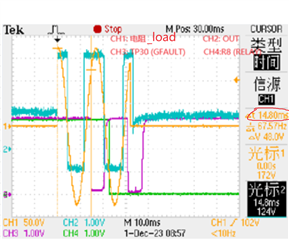

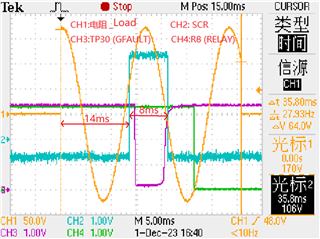

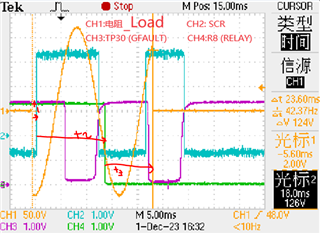

c. FT,NG_OUT, OUT, PH wave while power on 120Vac,60Hz:

Looking forward to your reply.

Best regards.

Lin