In the AWR2944 Datasheet it states:

Device architecture supports Four Digital Clock Comparators (EDCCs) and an internal

RCOSC. Dual functionality is provided by these modules – Clock detection and Clock

Monitoring.

EDCCA is dedicated for ADPLL/APLL lock detection monitoring, comparing the ADPLL/

APLL output divided version with the Reference input clock of the device. Failure detection

for EDCCA could be programmed to cause the device to go into limp mode.

Additionally, there is a provision to feed an external reference clock to monitor the internal

clock using the EDCCA.

EDCCB, EDCCC, EDCCD module is one which is available for user software. From the

list of clock options given in detailed spec, any two clocks can be compared. One example

usage is to compare the CPU clock with the Reference or internal RCOSC clock source.

Failure detection is indicated to the MSS R5F CPU via Error Signaling Module (ESM).

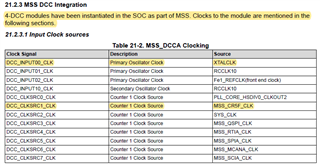

However in the TRM it shows the Clocks that can be compared for MSS_DCAA, MSS_DCAB, MSS_DCCC and MSS_DCCD as shown below:

Also two for DSS_DCAA and DSS_DCCB as shown:

The mmWave Radar document section 8.14, DCC_CLOCK_FREQ_MONITOR (see below) shows various clock pairs clock pairs which look at the frequency and measure the errors. It gives the Reference clock and the measured clock and the error threshold for each. It also gives the clock name and frequency for each. Through the API 0x01DC- AWR_MONITOR_DUAL_CLOCK_COMP_CONF_SB the different clock pairs can be enabled by setting bits b0, b1, b2, b3 or b4 to 1. The comparison results are in the monitoring report message.

Questions:

1. Why does the datasheet say DCAA is reserved and the TRM give options for clock comparision?

2. Why does the mmWave document define clock comparisons in section 8.14 for DCC pairs if they are also shown in the TRM as having various other input clock sources?

3. Section 21.2.2 Clock Source Selection for Counter0 and Counter1 states to reference the datasheet to identify the available options for selection the clock sources for both counters of the DCC module. The datasheet states "From the list of clock options given in detailed spec, any two clocks can be compared. One example usage is to compare the CPU clock with the Reference or internal RCOSC clock

source." However, the mmWave document gives clock pairs that can be turned on and off and reported.

3a) Which is document is correct and how are the pairs chosen?

3b) Are the ones in the mmWave document defaults and are they ready to enable (may required register configurations of course)?

3c) It appears that the documents are not clear and the TRM is for multiple products where the datasheet and mmWave may be more specific for the AWR2944, is that true?