Other Parts Discussed in Thread: OPT3101

Hi ti Team

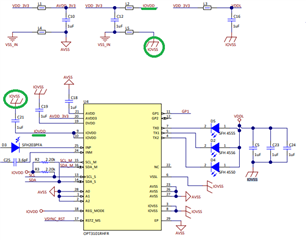

There is a difference in the ground reference for the capacitors on pins 9 and 10 of the OPT3101 IOVDD line.

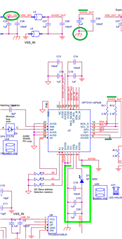

In the EVM design the capacitors are referenced to the ground of the VDD_LED line

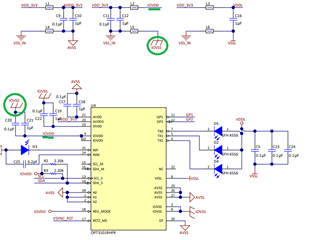

In one of the reference designs they are referenced to the IOVDD digital ground

I have two questions about how to reference these capacitors to ground.

What is the correct line to reference those capacitors to ground?

Are these capacitors necessary? Can we connect directly to the IOVDD_DUT line without placing the capacitors C29 and C30 First image?