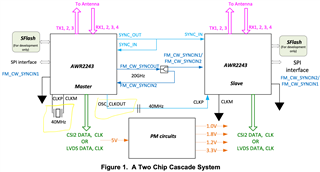

We have a cascaded radar designed based on the TI reference design and facing some issues with the bring up. We are in the process of configuring Master device.

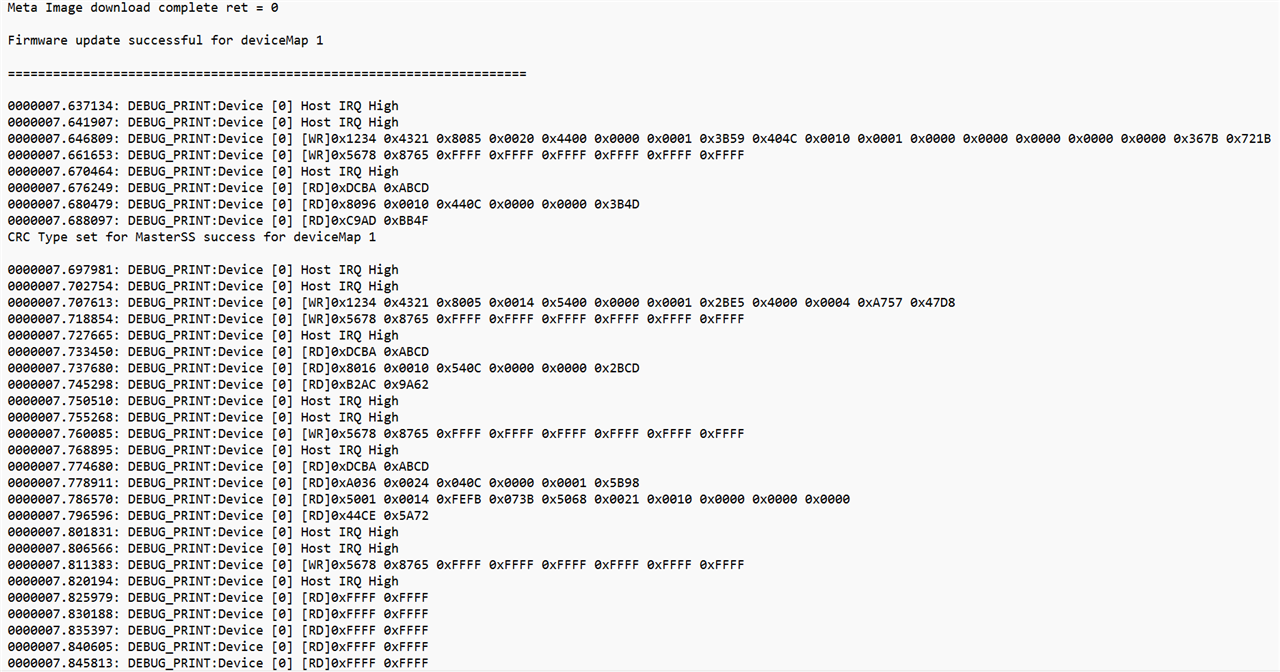

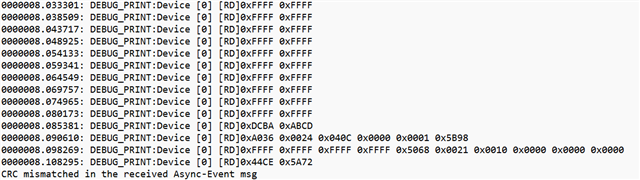

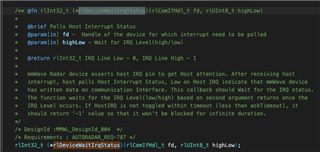

The issue is that after FW download gets completed, and during mmwl_rfenable, the device sends repetitive 0xFFFF to the host processor over SPI. The actual message arrives after lots of 0xFFFF but the application ends up with receiving checksum error which seem to be related to the junk 0xFFFF packets. We checked the MISO on a scope and it's all '1's for a long time.

Any idea what's going on?