Other Parts Discussed in Thread: LDC1612, LDC3114

Hello,

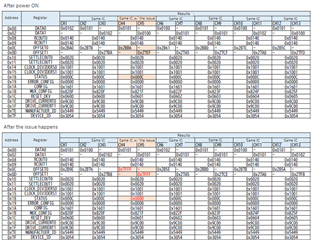

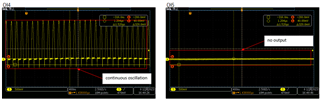

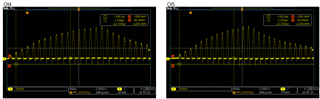

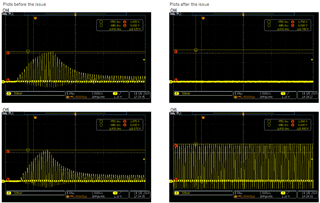

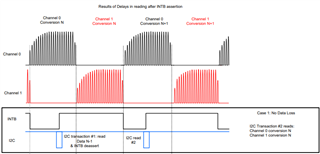

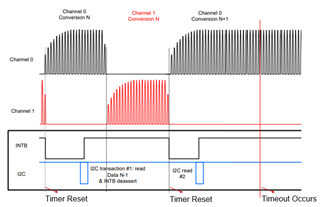

My customer has no output from the coil issue after a few hours from the power on. It happened a few days after the machines were delivered to the end customers which means the issue was found in the market. It can be reproduced even if they do power on again after power off. Would you please give me your comments how to find the root cause? There was no damage on both coils and ICs. I'm checking if they use an external OSC or internal one. If they do external, how the CLKIN would be when the issue happens. They haven't done ABA cross check yet.

Total samples : 1778

Samples w/ the issue : a few

LTC : 2CUA2HY(all of them)

2023.12.22_LDC1312_CoilNoOutput.xlsx

Best Regards,

Yoshikazu Kawasaki